## Advancing the Design of RFICs

#### INTRODUCTION

Analog Office® offers designers of RFICs and analog ICs an ease-to-use, flexible, accurate design environment within a single, integrated solution. The unique architecture of Analog Office software lets you control and seamlessly integrate best-in-class tools to capture, synthesize, simulate, optimize, layout, extract, and verify RFIC and analog designs from the system level through final tape-out. Analog Office streamlines designs, increases your productivity, and lets you get products to market faster.

"A key aim is to develop highly accurate models for transistors and passives such as spiral inductors at frequencies up to 40 GHz. Analog Office software enables us to accurately model active devices, passives, and interconnects on SoS so that our customers realize first-time-right designs."

Yash Moghe

Design Engineering Manager

Silanna

#### YOUR PRODUCTIVITY MATTERS

A Familiar Look'n'Feel – Zero Learning Curve: Since AWR was founded in 1994, our mission has been simple: to improve design productivity with a superior use-model that cuts complex tasks down to size. Whether you're just learning the software or embracing a new capability, every facet of Analog Office software is so well integrated that it's easy to forget the exceptionally powerful solvers and technology working behind the scenes.

Synchronized Data from Beginning to End: The Unified Data Model™ (UDM) is the basis of the AWR Design Environment™. This single, object-oriented database is synchronized at its core, not through multiple layers of software and translators. So whether you're driving the design from the schematic, simulation, or layout, the Analog Office design environment lets you take your ideas from concept through simulation and directly to fabrication - all in one platform.

Breadth of Solvers – Plug & Play: Only the AWR design environment lets you easily integrate software from third-party vendors like Synopsys' HSPICE into your design to enable you to choose the best tool for the task. Analog Office software also lets you export design layouts to an OpenAccess-based database so you can use the same libraries across a range of design tools from OpenAccess-based tool vendors. The result: big time savings to get your product through development faster.

## ANALOG OFFICE TOOLS, TECHNOLOGY & INNOVATIONS

#### Circuit Simulation Technology:

APLAC® "Battle tested" and foundry-proven in the design of Nokia® mobile phones for more than a decade, powerful APLAC engines deliver efficient harmonic balance and time-domain simulators specifically tailored for large-scale and extremely nonlinear RFIC designs. APLAC harmonic balance simulation is enhanced further by our patented Multi-Rate Harmonic Balance (MRHB™) technology for even more complex designs.

HSPICE Directly import HSPICE-formatted encrypted netlists into Analog Office software for immediate simulation/co-simulation within the AWR environment, allowing you to bring in legacy designs from your own firm, other design groups, or even outside companies.

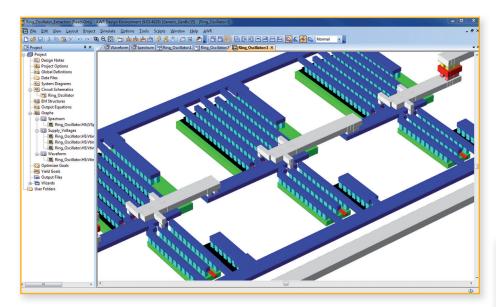

Analog Office software is a complete design environment offering all of the essential technologies: linear and nonlinear circuit simulators, EM analysis tools, layout-vs.-schematic checks, statistical design capabilities, and parametric cell libraries.

Ring oscillator layout in Analog Office.

#### **Electromagnetic Technology:**

Automatic Circuit Extraction (ACE™) Using layout-based models for circuit extraction, ACE dramatically reduces the time required to initially model complex interconnects by automatically identifying transmission lines from the layout and partitioning them into existing models.

AXIEM® Tailored for 3D high-frequency planar passives like spiral inductors, AXIEM delivers exceptionally accurate EM simulation that's fast and efficient for even the most complex designs.

Analyst™ For 3D on-chip interconnects like tapered vias, air-bridges, and finite dielectric/sidewalls, Analyst is only one click away from precise 3D finite element EM analysis.

EM Socket™ Integrate specialized "silicon-wise" third-party EM point tools from OEA into the design environment without leaving Analog Office.

## **Automation Technology:**

Intelligent Net (iNet™) Automatically tailors timing-driven and wire-driven digital design to high-frequency design.

DRC/LVS Access signed-off/approved links to EDA vendors from within Analog Office software. This gives you access to multiple sign-off verification flows, including PowerDRC/LVS, Mentor Graphics Calibre®, Cadence Assura, and even open-source ICED.

## **FEATURES AT A GLANCE**

- Transient/time-domain, AC and noise analysis using HSPICE and APLAC

- APLAC high-performance harmonic balance and transient solver technologies, including transient-assisted harmonic balance, multi-rate harmonic balance, and transient/timedomain (optional)

- iNet interconnect extraction technology

- ACE automatic circuit extraction technology for interconnect modeling

- AXIEM planar 3D EM analysis of on-chip passives (optional)

- Analyst 3D FEM EM analysis for 3D on-chip interconnects (optional)

- OEA International NET-AN for 3D

PLCK extraction

- EM Socket interface for integration with third-party EM tools

- DRC/LVS support for tools such as PowerDRC/LVS, Calibre, Assura, and ICED

- Seamless integration with AWR's Visual System Simulator™ software for system co-simulation

#### **CAPABILITIES**

- Linear and nonlinear circuit simulation

- Layout with parasitic extraction

- EM analysis

- Co-simulation with system tools

- Statistical design and design centering

- Links to back-end DRC/LVS

## **APPLICATIONS**

- RFIC

- Analog IC

# Advancing the wireless revolution®

## AWR SALES AND SUPPORT OFFICES

#### USA

## Corporate Headquarters

AWR Corporation 1960 E. Grand Avenue, Suite 430 El Segundo, CA 90245

+1 310 726 3000

+1 310 726 3005 (fax)

#### **AWR Silicon Valley**

+1 408 369 2180

#### **AWR Colorado**

+1 303 926 6817

## AWR Websites

www.awr.corp.com www.awr.tv

## Finland

AWR-APLAC Lars Sonckin kaari 10 FI-02600 Espoo, Finland +358 10 834 5900

#### France

AWR France (NI France)

2 rue Hennape

92735 Nanterre CEDEX, France

+33 1 70 36 19 63

## UK

AWR UK

2 Hunting Gate

Hitchin, Herts

SG4 OTJ, UK

+44 (0) 1462 428 428

## China

AWR China

Building 45

#1387 Zhangdong Road

Pudong District, Shanghai

P.R.China 201203

+86 21 5050 9800

#### Korea

AWR Korea Co. Ltd.

B-1412, Intellige-II, 24 Jeongja-dong,

Bundang-gu, Seongnam-si,

Gyeonggi-do, South Korea, 463-811

+82 31 603 7772

#### Japan

AWR Japan KK Level 5, 711 Building 7-11-18 Nishi-Shinjuku, Shinjuku-ku Tokyo 160-0023 Japan +81 3 5937 4803

Copyright © 2013 AWR Corporation. All rights reserved. AWR, Advancing the wireless revolution, APLAC, AXIEM and Analog Office are registered trademarks and the AWR logo, AWR Design Environment, Unified Data Model, Visual System Simulator, Analyst, ACE, MRHB, EM Socket, and iNet are trademarks of AWR Corporation. Other product and company names listed are trademarks or trade names of their respective companies.

BR-A0-2013.01.09