X = 2.6mm Y = 2.5mm

#### **Product Features**

■ RF frequency: 13.5 to 15.5 GHz

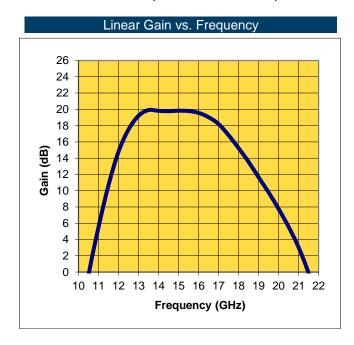

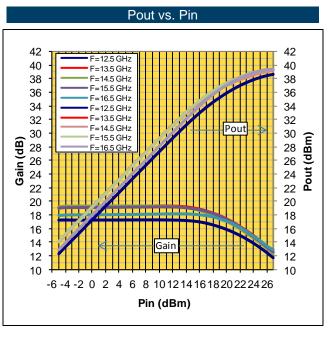

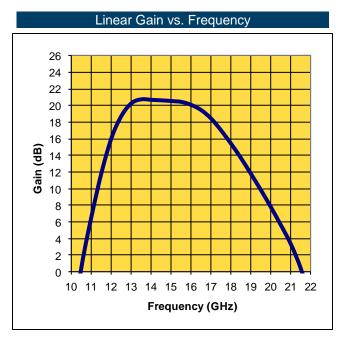

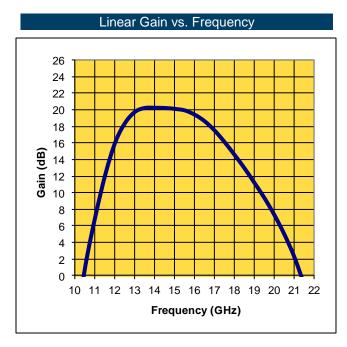

Linear Gain: 20 dB typ.

■ Psat: 39.5 dBm typ.

■ 0.2um GaN HEMT Process

■ 4 mil SiC substrate

■ DC Power: 24 VDC @ 880 mA

### **Applications**

- Point-to-Point Digital Radios

- Point-to-Multipoint Digital Radios

- SATCOM Terminals

### **Product Description**

The APN226 monolithic GaN HEMT amplifier is a broadband, two-stage power device, designed for use in SATCOM Terminals and point-to-point digital radios. To ensure rugged and reliable operation, HEMT devices are fully passivated. Both bond pad and backside metallization are Au-based that is compatible with epoxy and eutectic die attach methods.

#### Performance Characteristics (Ta = 25°C)

| Specification      | Min  | Тур  | Max  | Unit |

|--------------------|------|------|------|------|

| Frequency          | 13.5 |      | 15.5 | GHz  |

| Linear Gain        | 19   | 20   |      | dB   |

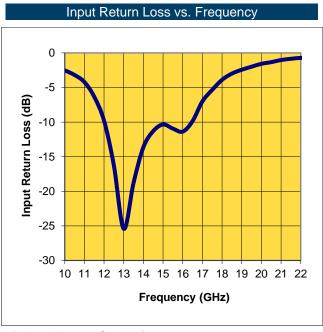

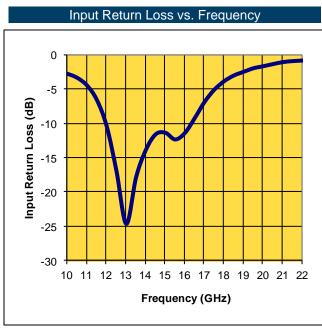

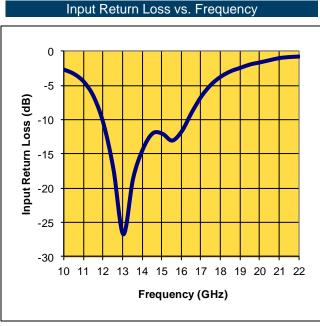

| Input Return Loss  | 9.5  | 12   |      | dB   |

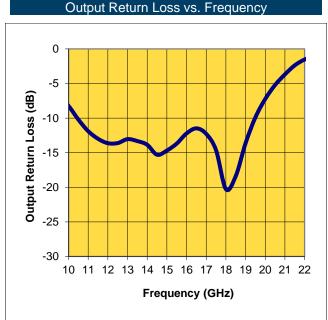

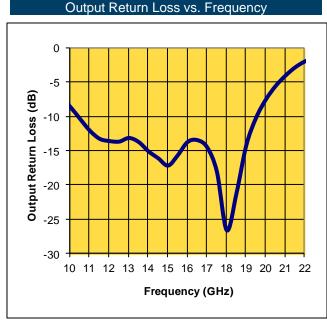

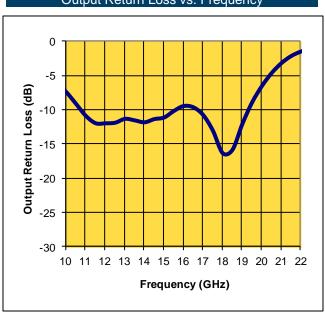

| Output Return Loss | 9.5  | 12   |      | dB   |

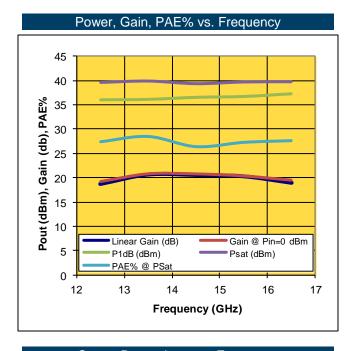

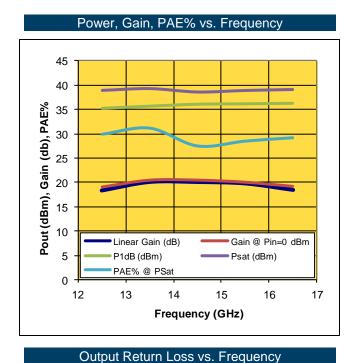

| P1dB (Pulsed)      |      | 36.5 |      | dBm  |

| Psat (Pulsed)      | 38.5 | 39.5 |      | dBm  |

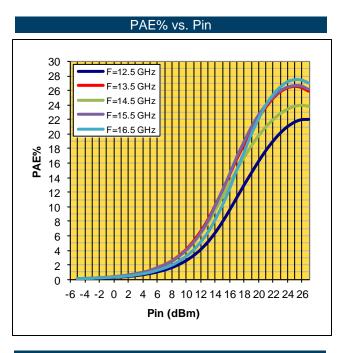

| PAE @ Psat         |      | 27   |      | %    |

| Vd1, Vd2           |      | 24   |      | V    |

| Vg1                |      | -3.5 |      | V    |

| Vg2                |      | -3.5 |      | V    |

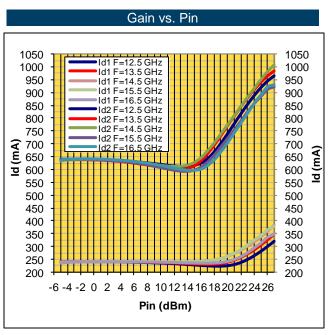

| ld1                |      | 240  |      | mA   |

| ld2                |      | 640  |      | mA   |

### Absolute Maximum Ratings (Ta = 25°C)

| Parameter         | Min | Max | Unit   |

|-------------------|-----|-----|--------|

| Vd1, Vd2          | 20  | 28  | V      |

| ld1               |     | 300 | mA     |

| ld2               |     | 800 | mA     |

| Vg1, Vg2          | -5  | 0   | V      |

| Input drive level |     | TBD | dBm    |

| Assy. Temperature |     | 300 | deg. C |

| (TBD seconds)     |     |     |        |

Production Datasheet Revision: July 2014

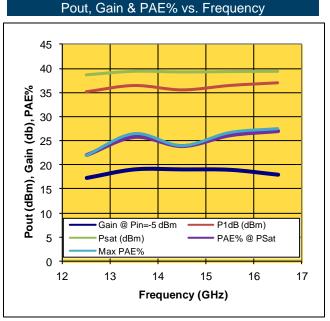

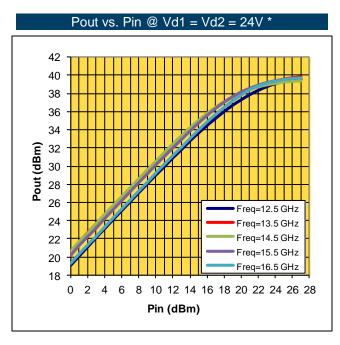

Measured On-Wafer Performance Characteristics (Typical Performance at 25°C) Vd1 = Vd2 = 24 V, Id1 = 240 mA, Id2 = 640 mA \*

<sup>\*</sup> Pulsed-Power On-Wafer

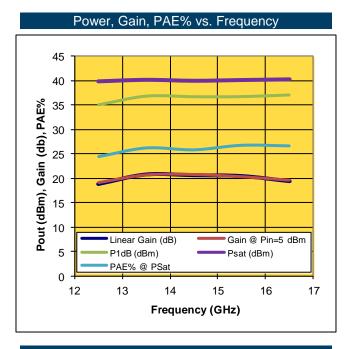

Measured Fixtured Performance Characteristics (Typical Performance at 25°C) Vd1 = Vd2 = 24 V Id1 = 240 mA, Id2 + Id2a = 640 mA \*\*

<sup>\*\*</sup> CW Fixtured

Production Datasheet Revision: July 2014

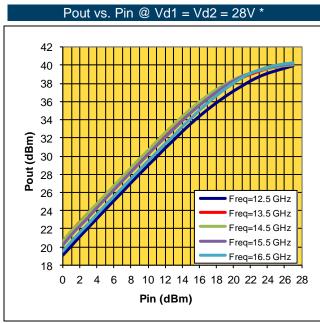

Measured On-Wafer Performance Characteristics (Typical Performance at 25°C) Vd1 = Vd2 = 28 V, Id1 = 240 mA, Id2 = 640 mA \*

<sup>\*</sup> Pulsed-Power On-Wafer

Production Datasheet Revision: July 2014

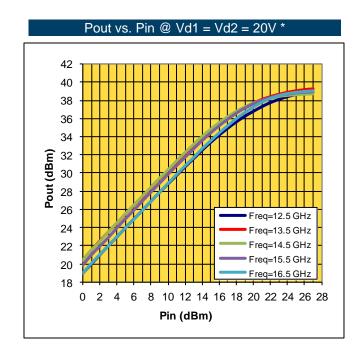

Measured On-Wafer Performance Characteristics (Typical Performance at 25°C) Vd1 = Vd2 = 20 V, Id1 = 240 mA, Id2 = 640 mA \*

<sup>\*</sup> Pulsed-Power On-Wafer

Measured On-Wafer Performance Characteristics (Typical Performance at 25°C) Id1 = 240 mA, Id2 = 640 mA

<sup>\*</sup> Pulsed-Power On-Wafer

Production Datasheet Revision: July 2014

#### **Thermal Properties**

Preliminary Thermal Properties with die mounted with 1mil 80/20 AuSn Eutectic to 25mil CuW Shim.

| Conditions               | Shim Boundary<br>Temperature | Junction<br>Temperature<br>Tjc | Thermal<br>Resistance<br>θjc |

|--------------------------|------------------------------|--------------------------------|------------------------------|

| Vd = 24V, Id1 = 380 mA * | 25 °C                        | 159.3 °C                       | 5.3 °C/W                     |

| ld2 + ld2a = 1008 mA *   | 50 °C                        | 196.1 °C                       | 5.8 °C/W                     |

| Pin=26.9 dBm             | 52.5 °C                      | 200.0 °C **                    | 5.83 °C/W                    |

| Pout=39.3 dBm            |                              |                                |                              |

<sup>\*</sup> Vd = 24.0 V, Idq1 = 240 mA, Id2q = 640 mA

<sup>\*\*</sup> Max recommended. Pre-qualification reliability testing indicates that MTTF in excess of 10<sup>5</sup> hours can be achieved by ensuring Tic is kept below 200°C.

<sup>\*</sup> Pulsed-Power On-Wafer

Production Datasheet Revision: July 2014

Measured On-Wafer Performance Characteristics (Typical Performance at 25°C) Vd1 = Vd2 = 24 V, Id1 = 240 mA, Id2 = 640 mA \*

| Freq GHz | S11 Mag | S11 Ang  | S21 Mag | S21 Ang  | S12 Mag | S12 Ang  | S22 Mag | S22 Ang  |

|----------|---------|----------|---------|----------|---------|----------|---------|----------|

| 8.0      | 0.788   | -175.150 | 0.056   | -69.128  | 0.002   | -149.171 | 0.624   | 145.730  |

| 8.5      | 0.792   | 177.549  | 0.054   | -50.533  | 0.003   | 100.724  | 0.595   | 126.795  |

| 9.0      | 0.782   | 169.211  | 0.081   | -26.971  | 0.005   | 98.959   | 0.528   | 102.406  |

| 9.5      | 0.767   | 160.468  | 0.171   | -9.116   | 0.006   | 84.303   | 0.455   | 75.452   |

| 10.0     | 0.743   | 148.982  | 0.425   | -13.926  | 0.002   | 39.443   | 0.386   | 43.034   |

| 10.5     | 0.685   | 136.345  | 1.041   | -37.959  | 0.004   | 45.457   | 0.307   | 6.553    |

| 11.0     | 0.606   | 120.640  | 2.053   | -72.411  | 0.005   | 78.299   | 0.252   | -24.432  |

| 11.5     | 0.461   | 101.870  | 3.697   | -111.478 | 0.004   | -19.991  | 0.229   | -50.326  |

| 12.0     | 0.305   | 82.279   | 5.877   | -156.942 | 0.006   | 22.788   | 0.215   | -71.266  |

| 12.5     | 0.140   | 57.241   | 7.944   | 156.616  | 0.006   | -11.884  | 0.209   | -83.304  |

| 13.0     | 0.033   | -7.924   | 9.536   | 110.075  | 0.004   | -57.805  | 0.223   | -95.152  |

| 13.5     | 0.107   | -101.508 | 10.221  | 65.248   | 0.007   | -38.639  | 0.217   | -111.473 |

| 14.0     | 0.192   | -119.288 | 10.070  | 25.403   | 0.002   | -170.834 | 0.204   | -115.664 |

| 14.5     | 0.245   | -134.405 | 10.015  | -11.781  | 0.002   | -161.559 | 0.172   | -119.745 |

| 15.0     | 0.273   | -143.902 | 10.061  | -47.813  | 0.002   | 64.799   | 0.174   | -116.071 |

| 15.5     | 0.254   | -141.837 | 9.979   | -83.956  | 0.004   | 125.238  | 0.186   | -115.597 |

| 16.0     | 0.259   | -133.613 | 9.615   | -121.442 | 0.004   | 51.271   | 0.205   | -120.465 |

| 16.5     | 0.348   | -122.232 | 8.968   | -159.474 | 0.005   | 5.375    | 0.227   | -134.886 |

| 17.0     | 0.477   | -126.098 | 8.065   | 162.641  | 0.005   | -6.692   | 0.200   | -153.352 |

| 17.5     | 0.569   | -132.862 | 6.836   | 125.406  | 0.008   | -53.726  | 0.144   | -179.669 |

| 18.0     | 0.662   | -139.509 | 5.673   | 90.341   | 0.004   | -176.720 | 0.062   | 117.915  |

| 18.5     | 0.725   | -148.466 | 4.646   | 55.355   | 0.003   | -141.496 | 0.101   | 25.350   |

| 19.0     | 0.769   | -155.321 | 3.720   | 20.982   | 0.007   | -102.598 | 0.209   | -8.918   |

| 19.5     | 0.807   | -160.898 | 2.978   | -12.195  | 0.002   | -161.597 | 0.322   | -25.318  |

| 20.0     | 0.845   | -166.839 | 2.350   | -46.408  | 0.006   | 111.398  | 0.433   | -39.840  |

| 20.5     | 0.865   | -171.744 | 1.839   | -81.138  | 0.002   | -135.188 | 0.545   | -54.065  |

| 21.0     | 0.895   | -176.622 | 1.404   | -118.400 | 0.005   | -152.650 | 0.647   | -65.974  |

| 21.5     | 0.910   | 178.326  | 1.002   | -159.002 | 0.005   | 76.670   | 0.747   | -76.390  |

| 22.0     | 0.925   | 173.710  | 0.627   | 159.607  | 0.009   | 87.246   | 0.832   | -89.068  |

| 22.5     | 0.923   | 169.561  | 0.341   | 122.484  | 0.005   | -140.272 | 0.873   | -99.611  |

| 23.0     | 0.931   | 165.925  | 0.173   | 92.298   | 0.010   | 115.686  | 0.903   | -108.257 |

| 23.5     | 0.934   | 162.265  | 0.087   | 68.801   | 0.005   | 68.757   | 0.918   | -116.042 |

| 24.0     | 0.940   | 159.140  | 0.043   | 52.012   | 0.007   | 102.110  | 0.933   | -122.749 |

<sup>\*</sup> Pulsed-Power On-Wafer

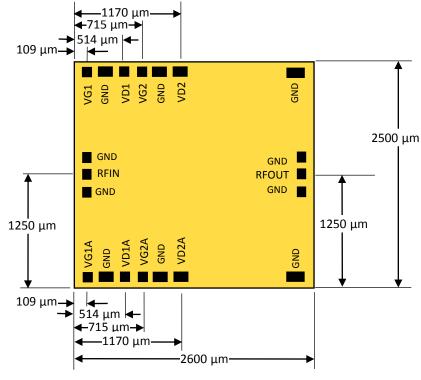

#### **Die Size and Bond Pad Locations (Not to Scale)**

$X = 2600 \pm 25 \mu m$   $Y = 2500 \pm 25 \mu m$ DC Bond Pad =  $100 \times 100 \pm 0.5 \mu m$ RF Bond Pad =  $100 \times 100 \pm 0.5 \mu m$ Chip Thickness =  $101 \pm 5 \mu m$

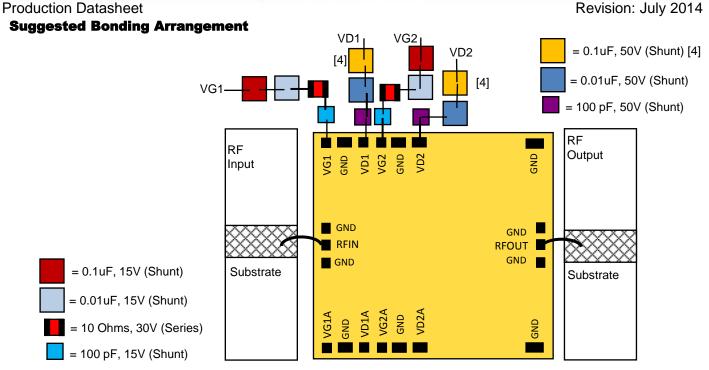

#### **Biasing/De-Biasing Details:**

APN226 can be biased from either the top or the bottom of the die.

Listed below are some guidelines for GaN device testing and wire bonding:

- a. Limit positive gate bias (G-S or G-D) to < 1V

- b. Know your devices' breakdown voltages

- c. Use a power supply with both voltage and current limit.

- d. With the power supply off and the voltage and current levels at minimum, attach the ground lead to your test fixture.

- i. Apply negative gate voltage (-5 V) to ensure that all devices are off

- ii. Ramp up drain bias to ∼10 V

- iii. Gradually increase gate bias voltage while monitoring drain current until 20% of the operating current is achieved

- iv. Ramp up drain to operating bias

- v. Gradually increase gate bias voltage while monitoring drain current until the operating current is achieved

- e. To safely de-bias GaN devices, start by debiasing output amplifier stages first (if applicable):

- i. Gradually decrease drain bias to 0 V.

- ii. Gradually decrease gate bias to 0 V.

- iii. Turn off supply voltages

- f. Repeat de-bias procedure for each amplifier stage

**Note:** APN226 can be biased from either the top or bottom and bias pads VG1A, VD1A, VG2A and VGD2A can be used as an alternative to the configuration shown.

#### **Recommended Assembly Notes**

- 1. Bypass caps should be 100 pF (approximately) ceramic (single-layer) placed no farther than 30 mils from the amplifier.

- 2. Best performance obtained from use of <10 mil (long) by 3 by 0.5 mil ribbons on input and output.

- 3. Part must be biased from both sides as indicated.

- 4. The 0.1uF, 50V capacitors are not needed if the drain supply line is clean. If Drain Pulsing of the device is to be used, do **NOT** use the 0.1uF, 50V Capacitors.

#### **Mounting Processes**

Most NGAS GaN IC chips have a gold backing and can be mounted successfully using either a conductive epoxy or AuSn attachment. NGAS recommends the use of AuSn for high power devices to provide a good thermal path and a good RF path to ground. Maximum recommended temp during die attach is 320°C for 30 seconds.

**Note**: Many of the NGAS parts do incorporate airbridges, so caution should be used when determining the pick up tool.

**CAUTION**: THE IMPROPER USE OF AuSn ATTACHMENT CAN CATASTROPHICALLY DAMAGE GaN CHIPS.

# PLEASE ALSO REFER TO OUR "Gan Chip Handling Application Note" BEFORE HANDLING, ASSEMBLING OR BIASING THESE MMICS!