### Product Description

The PE95420 is an RF SPDT (single pole double throw) switch and is available in a hermetically sealed ceramic package. The PE95420 is designed to cover a broad range of applications from 1 to 8500 MHz for use in various Hi-Rel industries and applications requiring broadband performance. It uses Peregrine's UltraCMOS™ process and features HaRP™ technology enhancements to deliver high linearity and exceptional harmonics performance. HaRP technology is an innovative feature of the UltraCMOS™ process providing upgraded linearity performance.

The PE95420 is an absorptive/non-reflective switch design which is an ideal termination method for RF elements in a system design. A single-pin 3.3V CMOS logic control in a single chip solution reduces the number of control lines.

### Typical Industries

- Medical

- Automotive

- Telecom Infrastructure

- Test Instrumentation

- Down-hole oil/gas

- Military

- Commercial space applications

#### RF SPDT Switch

Hermetically sealed ceramic package

1 – 8500 MHz

#### Features

- HaRP™-Technology-Enhanced

- Eliminates Gate and Phase Lag

- No Insertion Loss or Phase Drift

- High Linearity: 60 dBm IIP3

- Low Insertion Loss:

- 0.77 dB at 100 MHz

- 1.0 dB at 3000 MHz

- 1.15 dB at 6000 MHz

- 1.38 dB at 8500 MHz

- High Isolation (RF1-RF2)

- 86.5 dB at 100 MHz

- 48.2 dB at 3000 MHz

- 36.6 dB at 6000 MHz

- 27.8 dB at 8500 MHz

- Fast Switching Time

- 700 ns RF ON

- 300 ns RF OFF

- Ultra-Low Power Consumption

- 3.3  $\mu$ W @ 3.3 V

- 1 dB Compression Point of +33 dBm

- Single-pin 3.3 V CMOS logic control

- ESD tolerant to 2000 V HBM

- Absorptive/Non-Reflective

- Offered in a 7-lead Hermetic CSOIC Surface-Mount Package and in DIE form

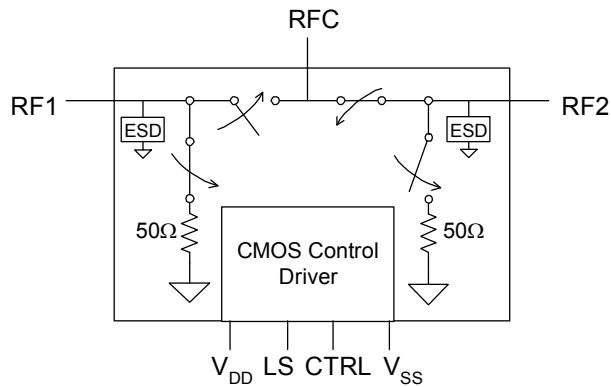

Figure 1. Functional Diagram

Figure 2. Package Type

7-lead CSOIC

**Table 1. Electrical Specifications @  $-40^{\circ}\text{C} \leq T \leq 85^{\circ}\text{C}$  &  $3.0\text{V} \leq \text{VDD} \leq 3.6\text{V}$**

| Parameter                           | Conditions                                 | Min  | Typical | Max  | Units |

|-------------------------------------|--------------------------------------------|------|---------|------|-------|

| Operational Frequency               |                                            | 1    |         | 8500 | MHz   |

| Insertion Loss                      | 100 MHz                                    |      | 0.77    | 0.95 | dB    |

|                                     | 3000 MHz                                   |      | 1       | 1.28 | dB    |

|                                     | 6000 MHz                                   |      | 1.15    | 1.42 | dB    |

|                                     | 8500 MHz                                   |      | 1.38    | 1.72 | dB    |

| Isolation – RFC to RF1              | 100 MHz                                    | 74   | 75.6    |      | dB    |

|                                     | 3000 MHz                                   | 46   | 47.4    |      | dB    |

|                                     | 6000 MHz                                   | 43.8 | 48      |      | dB    |

|                                     | 8500 MHz (note 2)                          | 31   | 38      |      | dB    |

| Isolation – RFC to RF2              | 100 MHz                                    | 73.7 | 75.4    |      | dB    |

|                                     | 3000 MHz                                   | 46.8 | 48.3    |      | dB    |

|                                     | 6000 MHz                                   | 45   | 52.1    |      | dB    |

|                                     | 8500 MHz (note 2)                          | 31   | 38      |      | dB    |

| Isolation – RF1 to RF2              | 100 MHz                                    |      | 86.5    |      | dB    |

|                                     | 3000 MHz                                   |      | 48.2    |      | dB    |

|                                     | 6000 MHz                                   |      | 36.6    |      | dB    |

|                                     | 8500 MHz                                   |      | 27.8    |      | dB    |

| Return Loss Active Port – ON State  | 100 MHz                                    |      | 21      |      | dB    |

|                                     | 3000 MHz                                   |      | 33      |      | dB    |

|                                     | 6000 MHz                                   |      | 20      |      | dB    |

|                                     | 8500 MHz                                   |      | 15      |      | dB    |

| Return Loss Active Port – OFF State | 100 MHz                                    |      | 20      |      | dB    |

|                                     | 3000 MHz                                   |      | 18      |      | dB    |

|                                     | 6000 MHz                                   |      | 15      |      | dB    |

|                                     | 8500 MHz                                   |      | 8       |      | dB    |

| Input 1 dB Compression (note 1)     | 8500 MHz                                   |      | 33      |      | dBm   |

| Input IP3                           | 8500 MHz, 18 dBm input power/tone          |      | 60      |      | dBm   |

| Switching Time                      | 50% CTRL to 90% of final value when RF ON  |      | 700     |      | ns    |

|                                     | 50% CTRL to 10% of final value when RF OFF |      | 300     |      | ns    |

Note: 1. Please note Maximum Operating Pin ( $50\Omega$ ) of  $+24\text{dBm}$  in *Table 3*.

2. Guaranteed but not tested

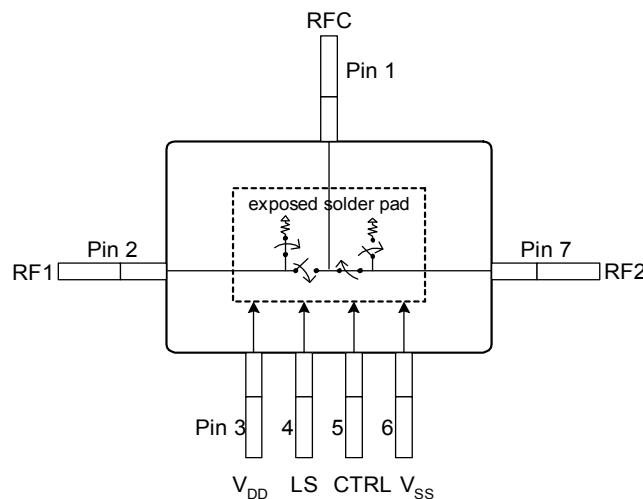

**Figure 3. Pin Layout (Top View)****Table 2. Pin Descriptions**

| Pin No. | Pin Name         | Description                                               |

|---------|------------------|-----------------------------------------------------------|

| 1       | RFC <sup>1</sup> | RF Common                                                 |

| 2       | RF1 <sup>1</sup> | RF Port 1                                                 |

| 3       | V <sub>DD</sub>  | Nominal 3.3 V supply connection                           |

| 4       | LS               | Selects the RF1 to RFC path<br>(See Table 6)              |

| 5       | CTRL             | Selects the RF2 to RFC path<br>(See Table 6)              |

| 6       | V <sub>SS</sub>  | Negative power supply. Apply nominal -3.3 V supply        |

| 7       | RF2 <sup>1</sup> | RF Port 2                                                 |

| paddle  | GND              | Exposed Solder Pad, grounded for proper device operation. |

Note 1: All RF pins must be DC blocked with an external series capacitor or held at 0 Vdc.

**Table 3. Operating Ranges**

| Parameter                                                                           | Min                 | Typ  | Max                 | Units |

|-------------------------------------------------------------------------------------|---------------------|------|---------------------|-------|

| V <sub>DD</sub> Positive Power Supply Voltage                                       | 3.0                 | 3.3  | 3.6                 | V     |

| V <sub>SS</sub> Negative Power Supply Voltage                                       | -3.6                | -3.3 | -3.0                | V     |

| I <sub>DD</sub> Power Supply Current<br>(V <sub>DD</sub> = 3.3V, LS or CTRL = 3.3V) |                     | < 1  |                     | µA    |

| I <sub>SS</sub> Power Supply Current<br>(V <sub>SS</sub> = -3.3V)                   |                     | < 1  |                     | µA    |

| Control Voltage High                                                                | 0.7xV <sub>DD</sub> |      |                     | V     |

| Control Voltage Low                                                                 |                     |      | 0.3xV <sub>DD</sub> | V     |

| Operating temperature range                                                         | -40                 |      | 85                  | °C    |

| RF Power In (50Ω):<br>1 MHz ≤ 8.5 GHz                                               |                     |      | 24                  | dBm   |

**Table 4. Post Radiation Table**

| Total Dose       | Parameter                               | Min  | Max | Units |

|------------------|-----------------------------------------|------|-----|-------|

| Post**<br>20krad | I <sub>DD</sub> Positive Supply Current |      | 100 | µA    |

|                  | I <sub>SS</sub> Negative Supply Current | -500 |     | µA    |

| Post 100krad     | I <sub>DD</sub> Positive Supply Current |      | 0.5 | mA    |

|                  | I <sub>SS</sub> Negative Supply Current | -5   |     | mA    |

\*\*Characterized but not tested

**Table 5. Absolute Maximum Ratings**

| Symbol           | Parameter/Conditions           | Min  | Max                   | Units |

|------------------|--------------------------------|------|-----------------------|-------|

| V <sub>DD</sub>  | Power supply voltage           | -0.3 | 4.0                   | V     |

| V <sub>C1</sub>  | Voltage on LS input            | -0.3 | V <sub>DD</sub> + 0.3 | V     |

| V <sub>C2</sub>  | Voltage on CTRL input          | -0.3 | V <sub>DD</sub> + 0.3 | V     |

| Θ <sub>JC</sub>  | Theta JC                       |      | 24                    | °C/W  |

| T <sub>ST</sub>  | Storage temperature range      | -65  | 150                   | °C    |

| V <sub>ESD</sub> | ESD voltage (Human Body Model) |      | 2000                  | V     |

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

### Electrostatic Discharge (ESD) Precautions

When handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rate specified.

### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS™ devices are immune to latch-up.

**Table 6. Truth Table**

| LS | CTRL | RFC-RF1 | RFC-RF2 | Logic State |

|----|------|---------|---------|-------------|

| 0  | 0    | off     | off     | OFF state   |

| 0  | 1    | off     | on      | RF2 active  |

| 1  | 0    | on      | off     | RF1 active  |

| 1  | 1    | N/A*    | N/A*    | N/A*        |

\* Invalid state that should not be used for normal operation.

### Exposed Solder Pad Connection

The exposed solder pad on the bottom of the package must be grounded for proper device operation.

### Switching Frequency

The PE95420 has a maximum 25 kHz switching rate.

## Performance Plots

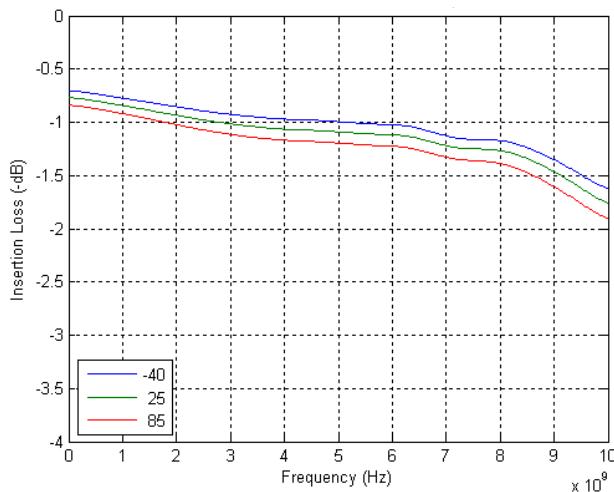

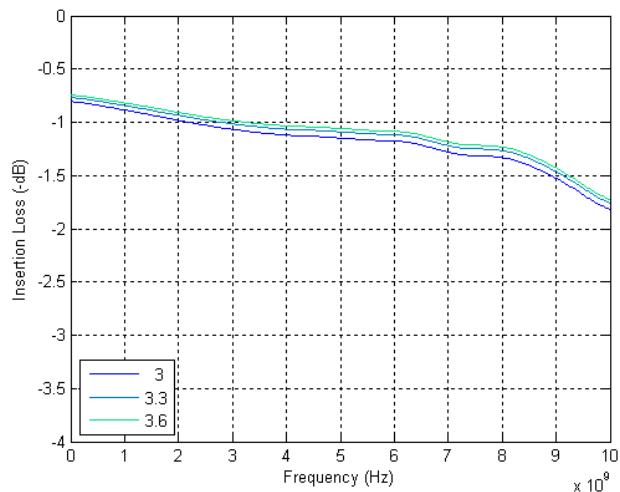

**Figure 4. Insertion Loss: RF1 @ 3.3 V**

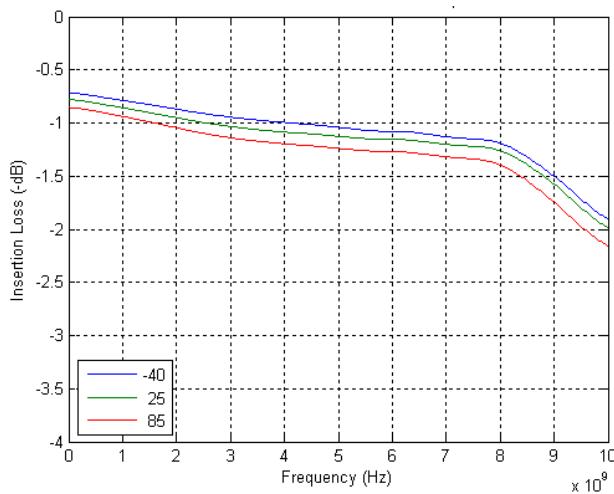

**Figure 5. Insertion Loss: RF1 @ 25 °C**

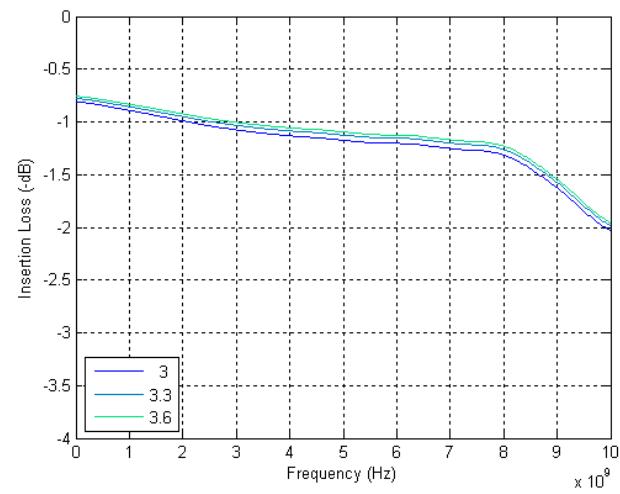

**Figure 6. Insertion Loss: RF2 @ 3.3 V**

**Figure 7. Insertion Loss: RF2 @ 25 °C**

## Performance Plots

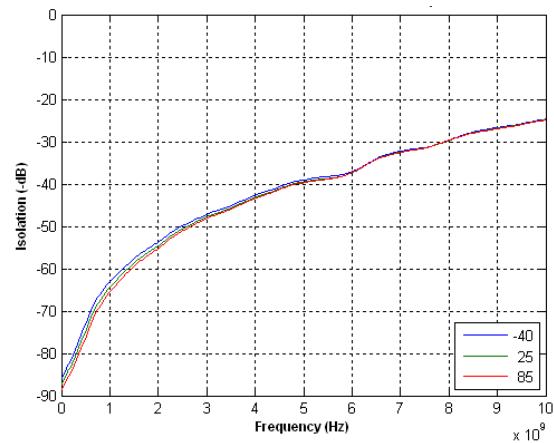

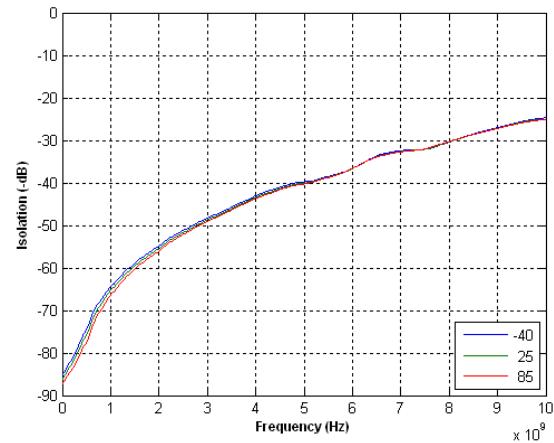

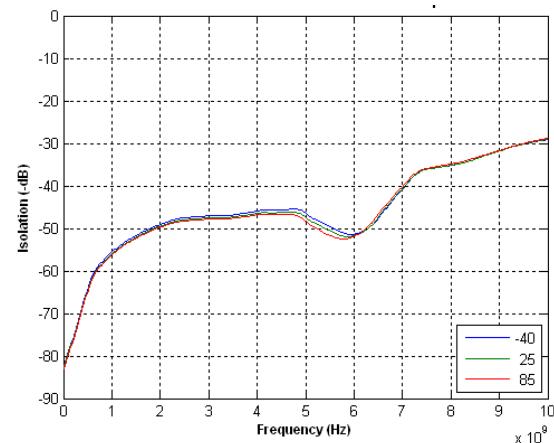

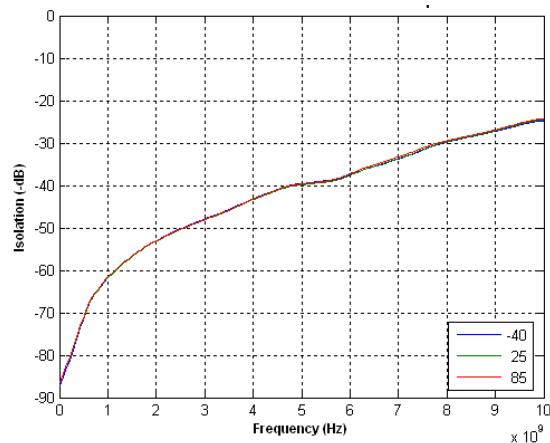

**Figure 8. Isolation: RF1-RF2, RF1 Active @  $V_{DD} = 3.3V$**

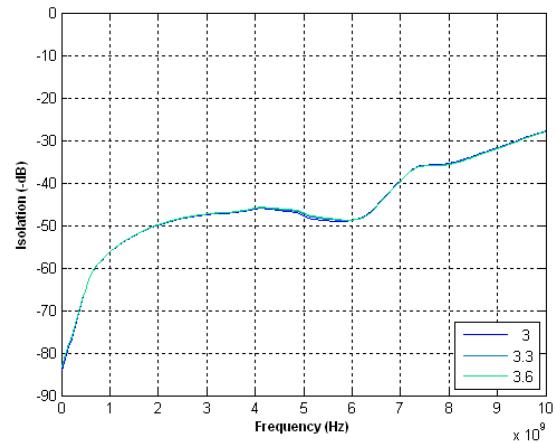

**Figure 9. Isolation: RF2-RF1, RF2 Active @  $V_{DD} = 3.3V$**

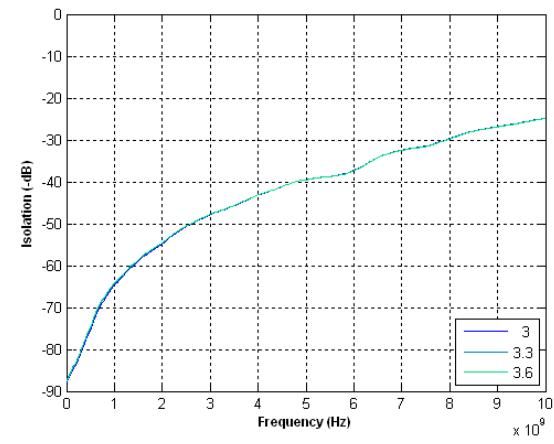

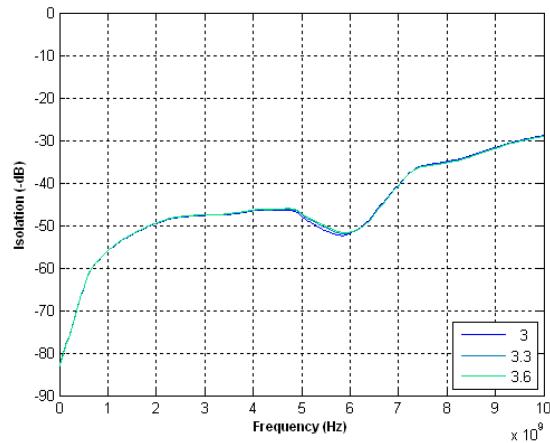

**Figure 10. Isolation: RF1-RF2, RF1 Active @  $25^{\circ}C$**

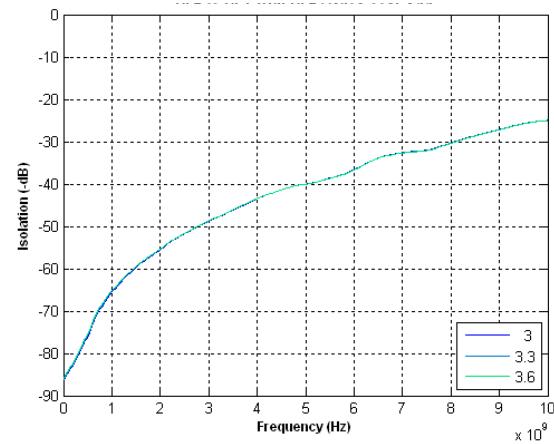

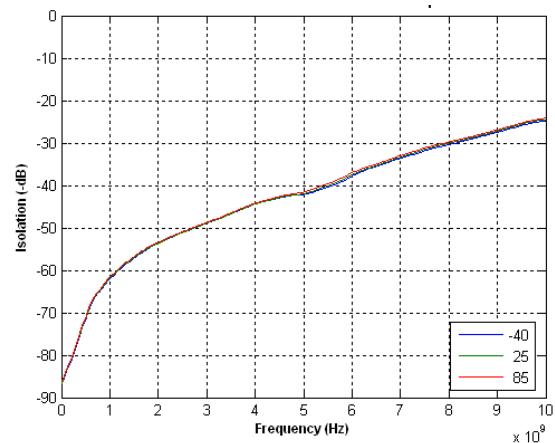

**Figure 11. Isolation: RF2-RF1, RF2 Active @  $25^{\circ}C$**

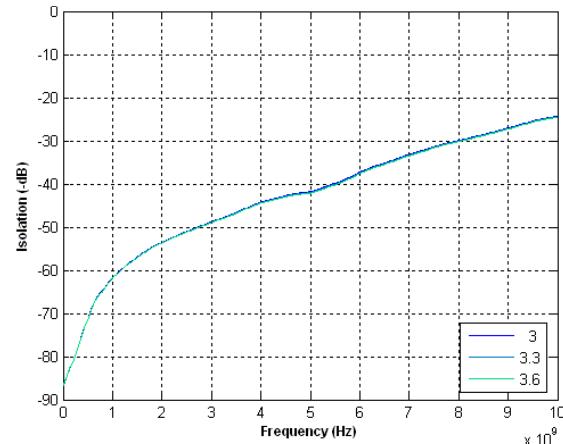

**Figure 12. Isolation: RFC-RF1, RF2 Active @  $V_{DD} = 3.3V$**

**Figure 13. Isolation: RFC-RF2, RF1 Active @  $V_{DD} = 3.3V$**

## Performance Plots

**Figure 14. Isolation: RFC-RF1, RF2 Active @ 25 °C**

**Figure 15. Isolation: RFC-RF2, RF1 Active @ 25 °C**

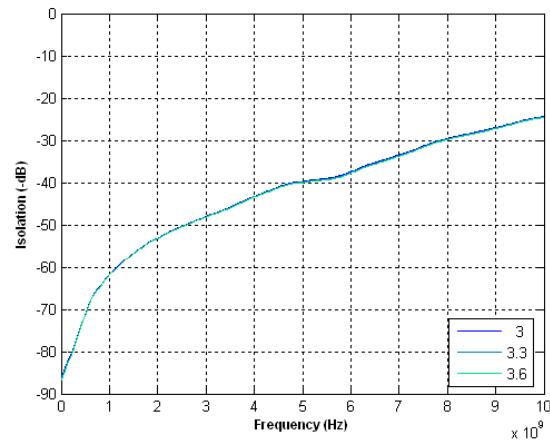

**Figure 16. Isolation: RFC-RF1, OFF state @ V<sub>DD</sub> = 3.3V**

**Figure 17. Isolation: RFC-RF2, OFF state @ V<sub>DD</sub> = 3.3V**

**Figure 18. Isolation: RFC-RF1, OFF state @ 25 °C**

**Figure 19. Isolation: RFC-RF2, OFF state @ 25 °C**

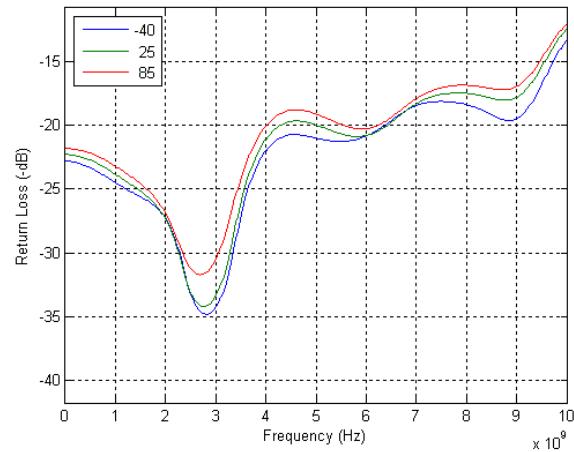

## Performance Plots

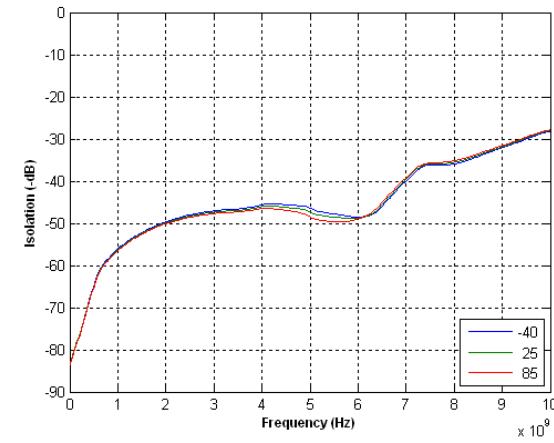

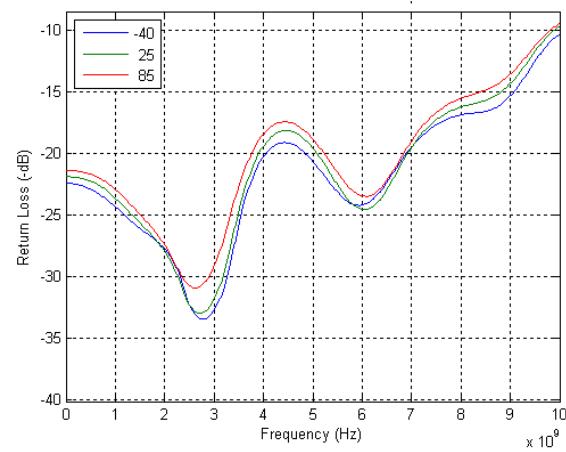

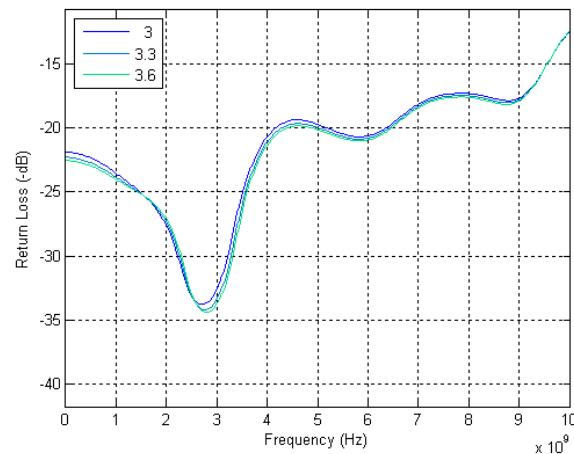

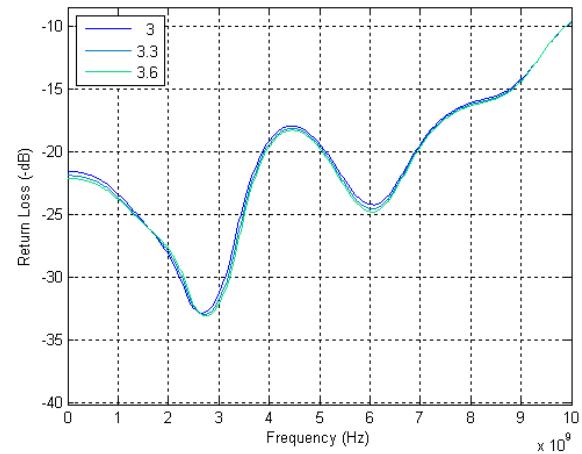

**Figure 20. Return Loss: RF1 @  $V_{DD} = 3.3V$**

**Figure 21. Return Loss: RF2 @  $V_{DD} = 3.3V$**

**Figure 22. Return Loss: RF1 @  $25^{\circ}C$**

**Figure 23. Return Loss: RF2 @  $25^{\circ}C$**

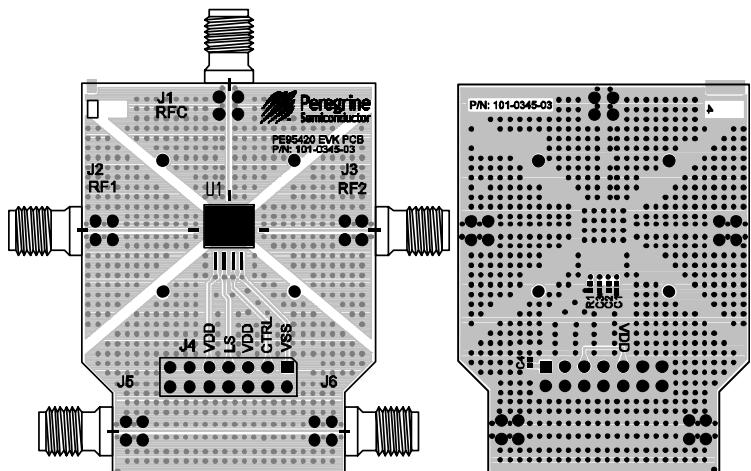

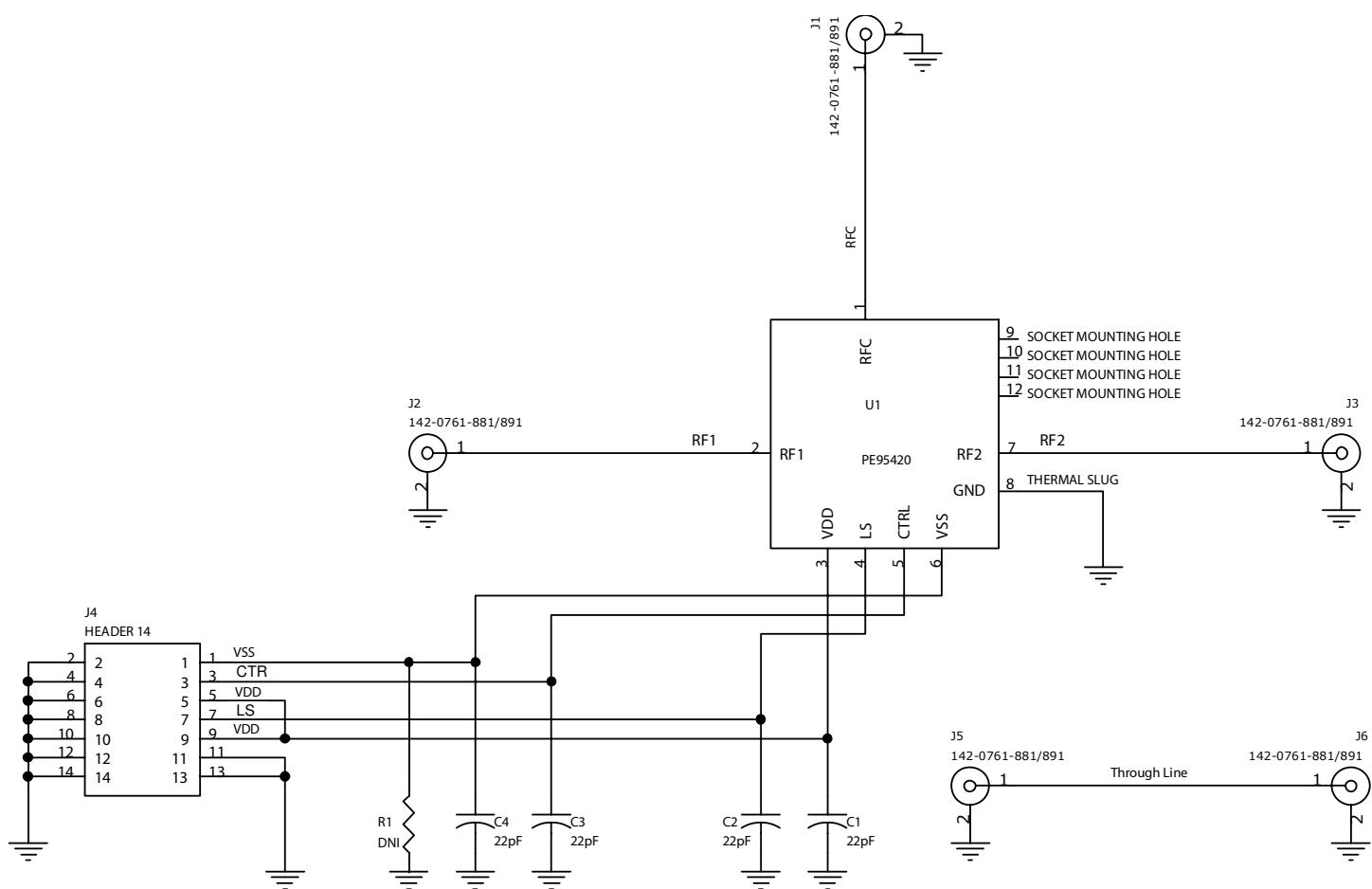

## Evaluation Board

The SPDT switch EK Board was designed to ease customer evaluation of Peregrine's PE95420. The RF common port is connected through a  $50\ \Omega$  transmission line via the top SMA connector, J1. RF1 and RF2 are connected through  $50\ \Omega$  transmission lines via SMA connectors J2 and J3, respectively. A through  $50\ \Omega$  transmission is available via SMA connectors J5 and J6. This transmission line can be used to estimate the loss of the PCB over the environmental conditions being evaluated.

The evaluation kit board is constructed of four metal layers. The dual clad top RF layer is Rogers RO4003 material with an 8 mil RF core and  $\epsilon_r = 3.55$ . The other two dielectric layers are FR4 for DC control and overall board strength with an cumulative board thickness of 62 mils. The RF transmission lines were designed using a Grounded co-planar waveguide with a linewidth of 15 mils and gap of 7 mils.

**Figure 24. Evaluation Board Layout**

Peregrine Specification 101-0345

**Figure 25. Evaluation Kit Schematic**

Peregrine Specification 102-0417

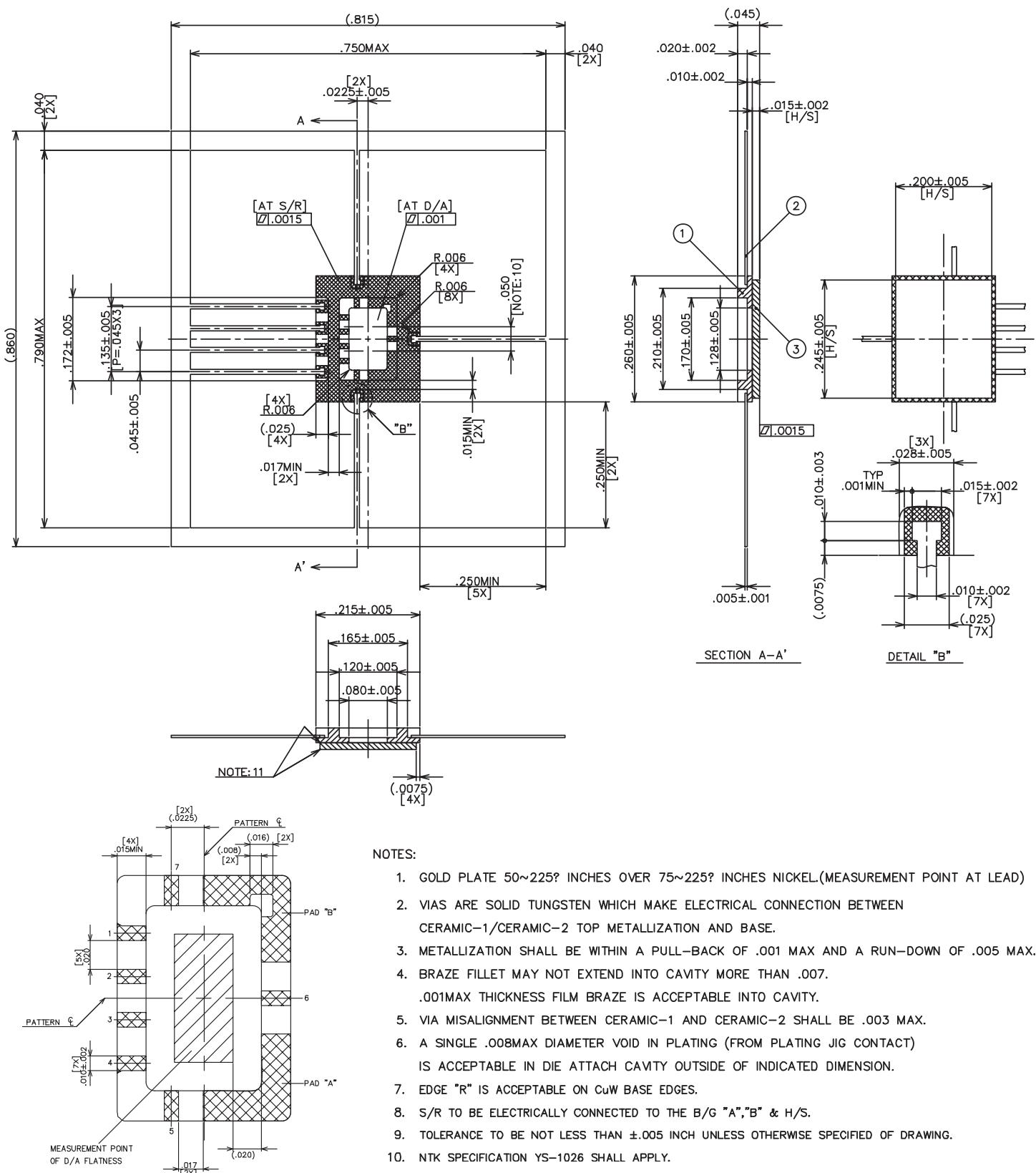

Figure 26. Package Drawing

7-lead CSOIC

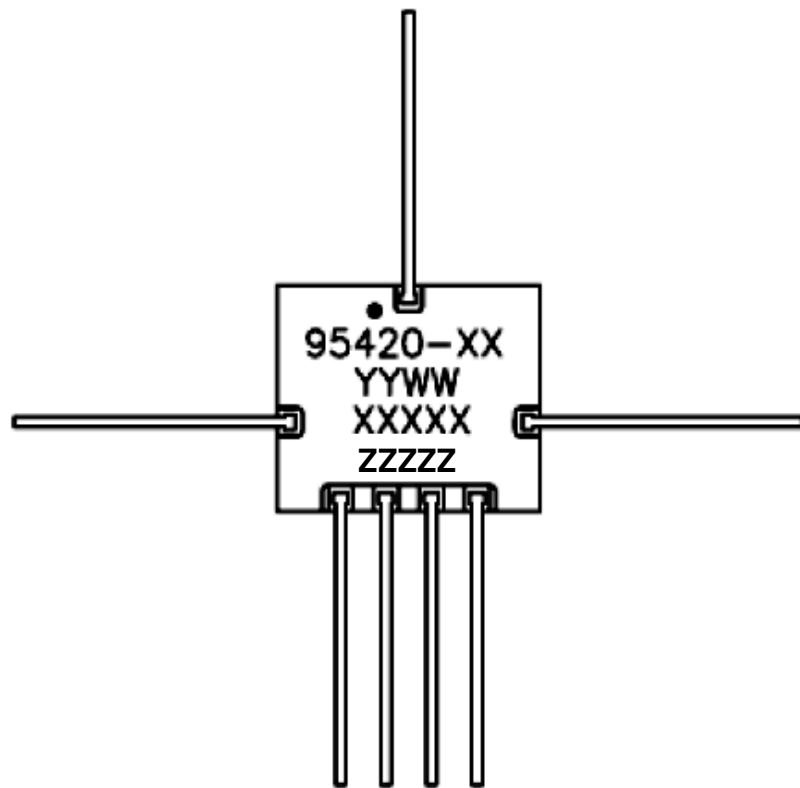

**Figure 27. Top Marking**

95420-XX= Part number e.g. 95420-11

XX will be specified by the PO and/or the Assembly Instructions

YYWW= Date Code-Last 2 digits of the year and work week

XXXXX = Lot Code

ZZZZZ = Serial Number

- = Pin 1 mark

**Table 7. Ordering Information**

| Order Code | Part Marking | Description                            | Package          | Shipping Method       |

|------------|--------------|----------------------------------------|------------------|-----------------------|

| 95420-01   | 95420-01     | PE95420-7CSOIC-50B Engineering Samples | 7-lead CSOIC     | 50 Count Trays        |

| 95420-11   | 95420-11     | PE95420-7CSOIC-50B Production Units    | 7-lead CSOIC     | 50 Count Trays        |

| 95420-99   |              | Production Die                         | Die              | 400 Units/Waffle Pack |

| 95420-00   | PE95420-EK   | PE95420 Evaluation Kit                 | Evaluation Board | 1 / Box               |

## Sales Offices

### *The Americas*

#### **Peregrine Semiconductor Corporation**

9380 Carroll Park Drive

San Diego, CA 92121

Tel: 858-731-9400

Fax: 858-731-9499

### *Europe*

#### **Peregrine Semiconductor Europe**

Bâtiment Maine

13-15 rue des Quatre Vents

F-92380 Garches, France

Tel: +33-1-4741-9173

Fax: +33-1-4741-9173

#### **High-Reliability and Defense Products**

*Americas*

San Diego, CA, USA

Phone: 858-731-9475

Fax: 848-731-9499

*Europe/Asia-Pacific*

Parc Cezanne 1

380 Avenue Archimède, Parc de la Duranne

13857 Aix-En-Provence Cedex 3, France

Phone: +33-4-4239-3361

Fax: +33-4-4239-7227

#### **Peregrine Semiconductor, Asia Pacific (APAC)**

Shanghai, 200040, P.R. China

Tel: +86-21-5836-8276

Fax: +86-21-5836-7652

#### **Peregrine Semiconductor, Korea**

#B-2607, Kolon Tripolis, 210

Geumgok-dong, Bundang-gu, Seongnam-si

Gyeonggi-do, 463-943 South Korea

Tel: +82-31-728-3939

Fax: +82-31-728-3940

#### **Peregrine Semiconductor K.K., Japan**

Teikoku Hotel Tower 10B-6

1-1-1 Uchisaiwai-cho, Chiyoda-ku

Tokyo 100-0011 Japan

Tel: +81-3-3502-5211

Fax: +81-3-3502-5213

For a list of representatives in your area, please refer to our

Web site at: [www.psemi.com](http://www.psemi.com)

## Data Sheet Identification

### **Advance Information**

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, and UTSi are registered trademarks and UltraCMOS, HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

### **Product Specification**

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).