## M21328 HD/SD and 2xHD-SDI Cable Driver

The M21328 is a high-speed, low-power, low-jitter cable drivers. It is designed to drive serial digital video data through  $75\Omega$  coaxial cable typically used in SMPTE and DVB-ASI video applications. The M21328 cable driver is optimized for performance from 143 Mbps up to 2970 Mbps. It has selectable slew rates for SD-SDI and HD-SDI applications.

The typical output rise/fall time of the M21328 is 100 ps for HD and 2xHD rates. It has a typical set slew rate of 600 ps at SD rates. The default output voltage swing is compliant with SMPTE 292M, 259M, 344M and 424M using a  $750\Omega \pm 1\%$  resistor. The M21328 supports a maximum single ended output swing of 1600 mVp-p, when configured appropriately.

The M21328 device is packaged in a new high performance 4x4 mm MLF package to simplify the PCB and reduce package parasitics with resulting improvements in Output Return Loss (ORL). It is available in an RoHS compliant package, that is backwards compatible with standard JEDEC SnPb processes.

The M21328 is pin compatible with the GS2978. It will also fit the footprint of the GS1578/1578A, but with the added feature of an Output Disable control pin.

### Applications

- Serial Routing Switchers,

- Production/Master Control Switchers

- Distribution Amplifiers

- Video Tape Recorders, ENG Edit decks, Cameras

- Broadcast video applications

- NLE's, MPEG Encoders/Decoders, format convertors etc.

### Standards Compliance

- SMPTE 292M, 259M, 344M, 424M

- DVB-ASI

### Features

- 2xHD, HD and SD operation

- 800 mVp-p single ended output swing (typical)

- 1600 mVp-p maximum single ended output swing

- SD/HD Slew Rate control

- 3.3V Supply

- Low  $P_{DISS}$  (144 mW @ 3.3V)

- Extended temp. range: -10 to 85°C

- RoHS package

- Output disable

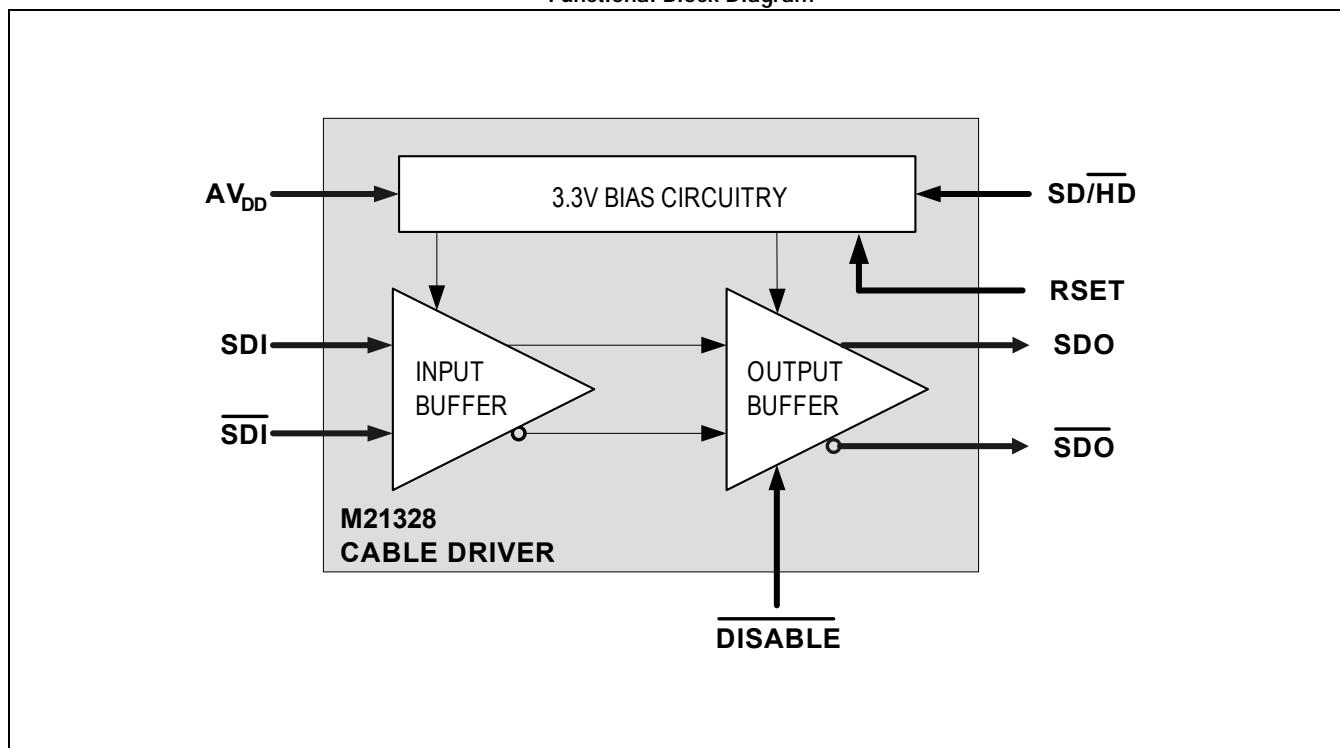

Functional Block Diagram

## Ordering Information

| Part Number                                                                                                                                                                                                                                          | Data Rates Supported | Package                            | Operating Temperature |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------|-----------------------|

| M21328G-12*                                                                                                                                                                                                                                          | 143–2970 Mbps        | 4x4 mm MLF—16pins (RoHS compliant) | -10 °C to 85 °C       |

| <b>NOTES:</b>                                                                                                                                                                                                                                        |                      |                                    |                       |

| * Consult the price list for exact part number when ordering.<br>* The letter 'G' designator after the part number indicates a RoHS-compliant package. Refer to <a href="http://www.mindspeed.com">www.mindspeed.com</a> for additional information. |                      |                                    |                       |

## Revision History

| Revision | Level   | Date           | Description                                                                                                                                                        |

|----------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | Advance | May 2007       | Initial Release.                                                                                                                                                   |

| B        | Release | July 2007      | Added $\theta_{JA}$ (Junction to ambient Thermal Resistance) to <a href="#">Table 1-2</a> .                                                                        |

| C        | Release | December 2007  | Output disable pin added.<br>Revised package dimensions.<br>HD/2xHD rise/fall time max changed to 135 ps.<br>Overshoot changed to +/-10%.                          |

| D        | Release | September 2008 | Table 1-3, removed pin 6 from the "Not Connected" list.<br>Table 1-5, removed 1485 Mbps from pin 10 description.<br>Removed section on Moisture Sensitivity Level. |

| E        | Release | November 2009  | Updated for -12 part.<br>Added marking diagram.                                                                                                                    |

### M21328 Marking Diagram

# Table of Contents

---

|                                                       |    |

|-------------------------------------------------------|----|

| Ordering Information . . . . .                        | 2  |

| Revision History . . . . .                            | 2  |

| Table of Contents . . . . .                           | 3  |

| List of Figures . . . . .                             | 4  |

| List of Tables . . . . .                              | 5  |

| 1.0 Product Specification . . . . .                   | 6  |

| 1.1 Absolute Maximum Ratings . . . . .                | 6  |

| 1.2 Recommended Operating Conditions . . . . .        | 6  |

| 1.3 DC Electrical Specifications . . . . .            | 7  |

| 1.4 Input/Output Level Specifications . . . . .       | 7  |

| 1.5 Package Specification . . . . .                   | 11 |

| 1.5.1 Mechanical Description . . . . .                | 11 |

| 1.5.1.1 Package Information . . . . .                 | 11 |

| 1.6 Manufacturability . . . . .                       | 13 |

| 1.6.1 Electrostatic Discharge . . . . .               | 13 |

| 1.6.2 Peak Reflow Temperature . . . . .               | 13 |

| 1.7 Design Considerations . . . . .                   | 13 |

| 2.0 Functional Description . . . . .                  | 14 |

| 2.1 Features . . . . .                                | 14 |

| 2.1.1 HD-SDI and SD-SDI Slew-rate Selection . . . . . | 14 |

| 2.1.2 Output Amplitude Adjustment . . . . .           | 14 |

| 2.2 Pin Definitions . . . . .                         | 15 |

| 2.2.1 High-speed Inputs . . . . .                     | 15 |

| 2.2.2 High-speed Outputs . . . . .                    | 16 |

| 2.2.3 M21328 Pin List . . . . .                       | 17 |

| Appendix . . . . .                                    | 18 |

| A.1 Glossary of Terms/Acronyms . . . . .              | 18 |

| A.2 Reference Documents . . . . .                     | 19 |

| A.2.1 External . . . . .                              | 19 |

## List of Figures

---

|             |                                                        |    |

|-------------|--------------------------------------------------------|----|

| Figure 1-1. | Output Symbols Definition .....                        | 10 |

| Figure 1-2. | M21328 Pin Out .....                                   | 11 |

| Figure 1-3. | Package Drawing (4x4 mm MLF Package) .....             | 12 |

| Figure 2-1. | Typical Input Circuit—AC Coupled .....                 | 15 |

| Figure 2-2. | Typical Input Circuit—DC Coupled .....                 | 15 |

| Figure 2-3. | Typical Output Matching/Back-termination Circuit ..... | 16 |

## List of Tables

---

|            |                                                                  |    |

|------------|------------------------------------------------------------------|----|

| Table 1-1. | Absolute Maximum Ratings .....                                   | 6  |

| Table 1-2. | Recommended Operating Conditions .....                           | 6  |

| Table 1-3. | Power DC Electrical Specifications .....                         | 7  |

| Table 1-4. | CMOS Input Electrical Specifications .....                       | 7  |

| Table 1-5. | High-Speed Input Electrical Specifications .....                 | 8  |

| Table 1-6. | Cable Driver Output Electrical Specifications (SD/HD/2xHD) ..... | 9  |

| Table 2-1. | Output Swing vs. Supply and Termination Voltage .....            | 14 |

| Table 2-2. | Interface Pins .....                                             | 17 |

| Table 2-3. | Power Pins .....                                                 | 17 |

| Table 2-4. | High-speed Signal Pins .....                                     | 17 |

| Table 2-5. | Control Pins .....                                               | 17 |

# 1.0 Product Specification

---

## 1.1 Absolute Maximum Ratings

**Table 1-1. Absolute Maximum Ratings**

| Symbol       | Parameter                             | Minimum         | Maximum          | Units |

|--------------|---------------------------------------|-----------------|------------------|-------|

| $V_{DD}$     | Power                                 | $AV_{SS} - 0.5$ | $AV_{SS} + 3.47$ | V     |

| $V_{IOAM}$   | Any I/O Pin                           | $AV_{SS} - 0.5$ | $AV_{DD} + 0.5$  | V     |

| $T_{STORE}$  | Storage Temperature                   | -65             | +150             | °C    |

| $ESD_{HBML}$ | Human Body Model (low-speed)          | 2000            | —                | V     |

| $ESD_{HBMH}$ | Human Body Model (high-speed outputs) | 2000            | —                | V     |

| $ESD_{CDM}$  | Charge Device Model                   | 500             | —                | V     |

**NOTE:**

1. No Damage.

## 1.2 Recommended Operating Conditions

**Table 1-2. Recommended Operating Conditions**

| Symbol          | Parameter                              | Notes | Minimum        | Typical | Maximum | Units |

|-----------------|----------------------------------------|-------|----------------|---------|---------|-------|

| $AV_{DD}$       | $AV_{DD}$ Power                        | 1     | —              | 3.3     | —       | V     |

| $AV_{SS}$       | $AV_{SS}$ Ground                       | —     | —              | 0       | —       | V     |

| $T_A$           | Ambient Temperature                    | —     | -10            | —       | +85     | °C    |

| $\theta_{JA}$   | Junction to ambient Thermal Resistance |       | —              | 61      | —       | °C/W  |

| $AV_{DD\_TERM}$ | 75Ω Output Termination Voltage         |       | See Table 2-1. |         |         |       |

**NOTES:**

1. ±5% is allowed from nominal supply.

## 1.3 DC Electrical Specifications

**Table 1-3. Power DC Electrical Specifications**

| Symbol         | Parameter                                                     | Notes   | Minimum | Typical | Maximum | Units |

|----------------|---------------------------------------------------------------|---------|---------|---------|---------|-------|

| $I_{DD}$       | Supply Current                                                | 1, 2    | —       | 27      | 36      | mA    |

| $I_{DDTERM}$   | Current in external termination resistors                     | 1, 2, 3 | —       | 22      | —       | mA    |

| $P_{DISSINT1}$ | Power dissipation ( $AV_{DD} = 3.3V$ , $AV_{DDTERM} = 3.3V$ ) | 1, 2, 5 | —       | 144     | —       | mW    |

| $P_{DISSINT1}$ | Power dissipation ( $AV_{DD} = 3.3V$ , $AV_{DDTERM} = 5.0V$ ) | 1, 2, 5 | —       | 181     | —       | mW    |

| $P_{DISSTOT1}$ | Power dissipation ( $AV_{DD} = 3.3V$ , $AV_{DDTERM} = 3.3V$ ) | 1, 2, 4 | —       | 162     | —       | mW    |

| $P_{DISSTOT1}$ | Power dissipation ( $AV_{DD} = 3.3V$ , $AV_{DDTERM} = 5.0V$ ) | 1, 2, 4 | —       | 199     | —       | mW    |

**NOTES:**

1. Recommended operating conditions—see [Table 1-2](#).

2. 800 mV standard SMPTE swing, terminated as in [Figure 2-3](#).

3. A portion of the power will be dissipated in the external  $750\Omega$  termination ( $P_{EXT} = V_{OD} \times I_{TERM}$ ).

4.  $P_{DISSTOT} = AV_{DD} \times I_{DD} + AV_{DDTERM} \times I_{TERM}$ .

5.  $P_{DISSINT} = P_{DISSTOT} - P_{EXT}$ .

## 1.4 Input/Output Level Specifications

**Table 1-4. CMOS Input Electrical Specifications**

| Symbol   | Parameter                  | Notes | Minimum               | Typical | Maximum               | Units   |

|----------|----------------------------|-------|-----------------------|---------|-----------------------|---------|

| $V_{IH}$ | Input Logic High Voltage   | 1     | $0.75 \times AV_{DD}$ | —       | $AV_{DD} + 0.3$       | V       |

| $V_{IL}$ | Input Logic Low Voltage    | 1     | 0                     | —       | $0.25 \times AV_{DD}$ | V       |

| $I_{IH}$ | Input Current (logic High) | 1     | -100                  | —       | 100                   | $\mu A$ |

| $I_{IL}$ | Input Current (logic Low)  | 1     | -100                  | —       | 100                   | $\mu A$ |

**NOTE:**

1. Specified at recommended operating condition—see [Table 1-2](#).

**Table 1-5. High-Speed Input Electrical Specifications**

| Symbol           | Parameter                                 | Notes   | Minimum | Typical | Maximum                | Units |

|------------------|-------------------------------------------|---------|---------|---------|------------------------|-------|

| DR <sub>IN</sub> | Input Bit Rate                            | 1, 2    | 0       | —       | 2970                   | Mbps  |

| V <sub>ID</sub>  | Input Differential Voltage (peak to peak) | 1, 3, 4 | 100     | —       | 2000                   | mV    |

| V <sub>CM</sub>  | Input Common-Mode Voltage                 | 1       | 1200    | —       | AV <sub>DD</sub>       | mV    |

| V <sub>IH</sub>  | Maximum Input High Voltage                | 1       | —       | —       | AV <sub>DD</sub> + 400 | mV    |

| V <sub>IL</sub>  | Minimum Input Low Voltage                 | 1       | 1.2     | —       | —                      | V     |

| R <sub>IN</sub>  | Single-ended input impedance              | 1       | —       | 13.33   | 20                     | kΩ    |

**NOTES:**

1. Specified at recommended operation conditions—see [Table 1-2](#).

2. Part is DC coupled at the input.

3. Example 1200 mV<sub>pp</sub> differential = 600 mV<sub>pp</sub> for each single-ended terminal.

4. Minimum input level defined as BER  $\leq 10^{-12}$ .

**Table 1-6. Cable Driver Output Electrical Specifications (SD/HD/2xHD)**

| Symbol                                                                                                                                                                                                                                                                | Parameter                                                                    | Notes         | Minimum | Typical | Maximum | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------|---------|---------|---------|-------|

| DR <sub>OUT</sub>                                                                                                                                                                                                                                                     | Output Bit Rates                                                             | 1, 5          | 0       | —       | 2970    | Mbps  |

| t <sub>r</sub> /t <sub>f</sub>                                                                                                                                                                                                                                        | SD Rise/Fall Time (20–80%)                                                   | 1, 3, 5       | 400     | 600     | 800     | ps    |

|                                                                                                                                                                                                                                                                       | HD/2xHD Rise/Fall Time (20–80%)                                              | 1, 3, 5       | —       | 100     | 135     | ps    |

| t <sub>r</sub> /t <sub>f</sub> <sub>IMM</sub>                                                                                                                                                                                                                         | Rise/fall mismatch (HD/2xHD Rate)                                            | 1, 2, 5       | —       | 10      | 30      | ps    |

|                                                                                                                                                                                                                                                                       | Rise/fall mismatch (SD Rate)                                                 | 1, 2, 5       | —       | 40      | 100     | ps    |

| V <sub>O</sub>                                                                                                                                                                                                                                                        | Single-ended voltage swing range p–p                                         | 1, 2, 4, 5    | 500     | 800     | 1600    | mV    |

| V <sub>OTOL</sub>                                                                                                                                                                                                                                                     | Swing Level output variation at 800 mVpp<br>[RSET = 750Ω ±1%] (Single-Ended) | 1, 2, 3, 5    | -7      | —       | +7      | %     |

| V <sub>OS</sub>                                                                                                                                                                                                                                                       | Overshoot/Undershoot                                                         | 1, 2, 5       | -10     | —       | +10     | %     |

| JAO <sub>PP</sub>                                                                                                                                                                                                                                                     | Additive Output Jitter (HD/2xHD rate)                                        | 1, 5, 8       | —       | 20      | 30      | ps    |

|                                                                                                                                                                                                                                                                       | Additive Output Jitter (SD rate)                                             | 1, 5, 8       | —       | 40      | 60      | ps    |

| DCD <sub>0</sub>                                                                                                                                                                                                                                                      | Duty Cycle Distortion (HD/2xHD Rate)                                         | 1, 2, 5, 6, 8 | —       | 15      | 30      | ps    |

|                                                                                                                                                                                                                                                                       | Duty Cycle Distortion (SD Rate)                                              | 1, 2, 5, 6, 8 | —       | 20      | 70      | ps    |

| S <sub>22</sub>                                                                                                                                                                                                                                                       | Output Return Loss (5 MHz to 1.5 GHz)                                        | 1, 2, 5, 7    | 15      | —       | —       | dB    |

| S <sub>22</sub>                                                                                                                                                                                                                                                       | Output Return Loss (5 MHz to 3.0 GHz)                                        | 1, 2, 5, 7    | 10      | —       | —       | dB    |

| <b>NOTES:</b>                                                                                                                                                                                                                                                         |                                                                              |               |         |         |         |       |

| 1. Entire table specified at recommended operating condition with 400 mV <sub>P-P</sub> differential input—see <a href="#">Table 1-2</a> .                                                                                                                            |                                                                              |               |         |         |         |       |

| 2. Specification verified at 800 mVpp output with 1m cable on MSPD test board. System results may vary.                                                                                                                                                               |                                                                              |               |         |         |         |       |

| 3. Rated at nominal SMPTE 800 mV output swing level (using a 750Ω ±1% resistor at RSET).                                                                                                                                                                              |                                                                              |               |         |         |         |       |

| 4. Output stage is an open collector differential pair, actual swing dependant on IC supply voltage and external termination voltage.                                                                                                                                 |                                                                              |               |         |         |         |       |

| 5. Into 75Ω back termination and 75Ω load and appropriate external termination voltage, see <a href="#">Table 2-1</a> , <a href="#">Figure 2-3</a> .                                                                                                                  |                                                                              |               |         |         |         |       |

| 6. Duty Cycle Distortion (DCD) is defined as the difference in the intrinsic jitter at the 50% voltage level and the intrinsic jitter at the rising/falling edge crossing point. If the rising/falling edge crossing point is at the 50% voltage level, then DCD = 0. |                                                                              |               |         |         |         |       |

| 7. Measured under DC conditions that simulate AC coupling, V <sub>T</sub> = 3.3V.                                                                                                                                                                                     |                                                                              |               |         |         |         |       |

| 8. Measured using a "1010" data pattern.                                                                                                                                                                                                                              |                                                                              |               |         |         |         |       |

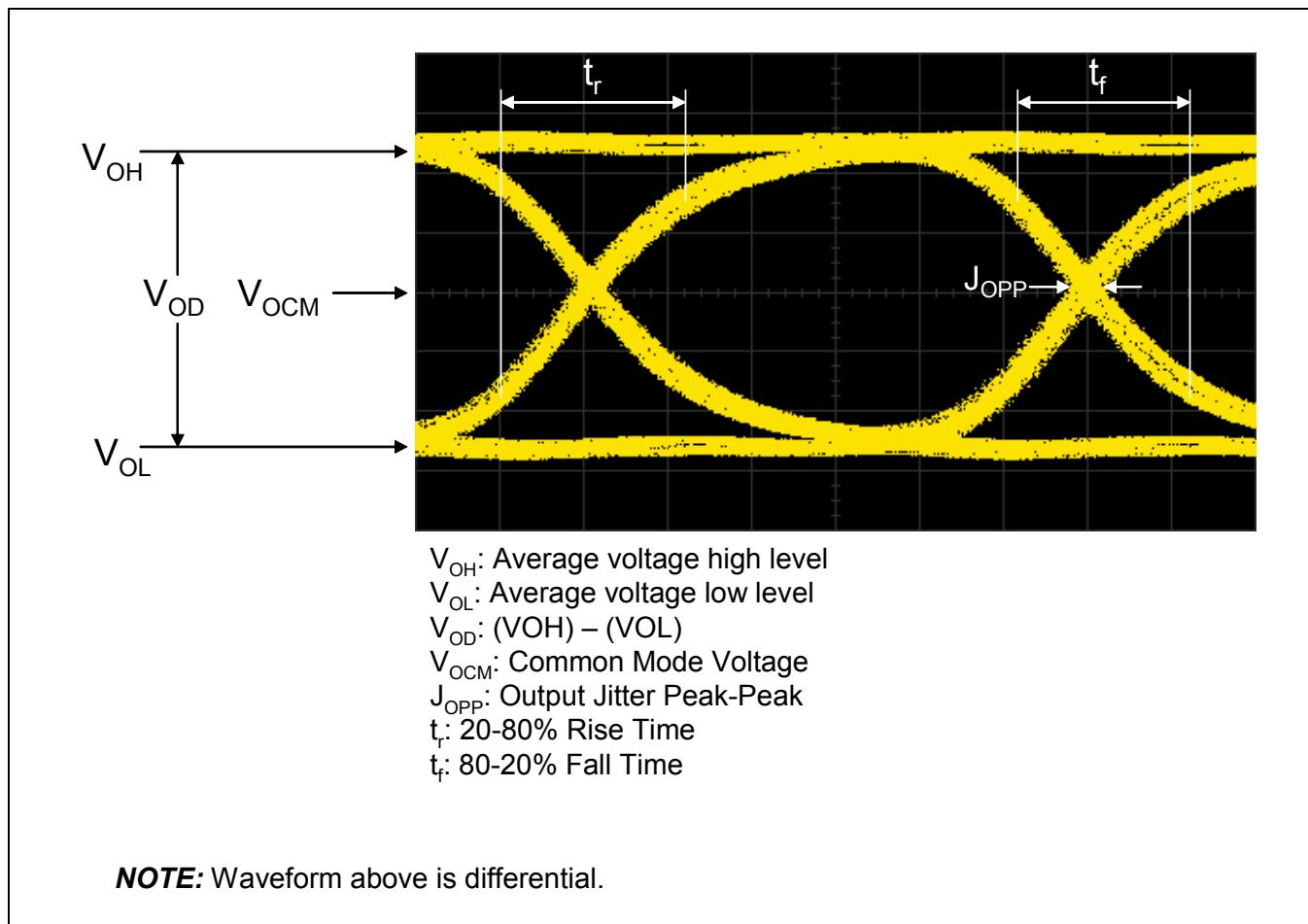

Figure 1-1. Output Symbols Definition

## 1.5 Package Specification

### 1.5.1 Mechanical Description

#### 1.5.1.1 Package Information

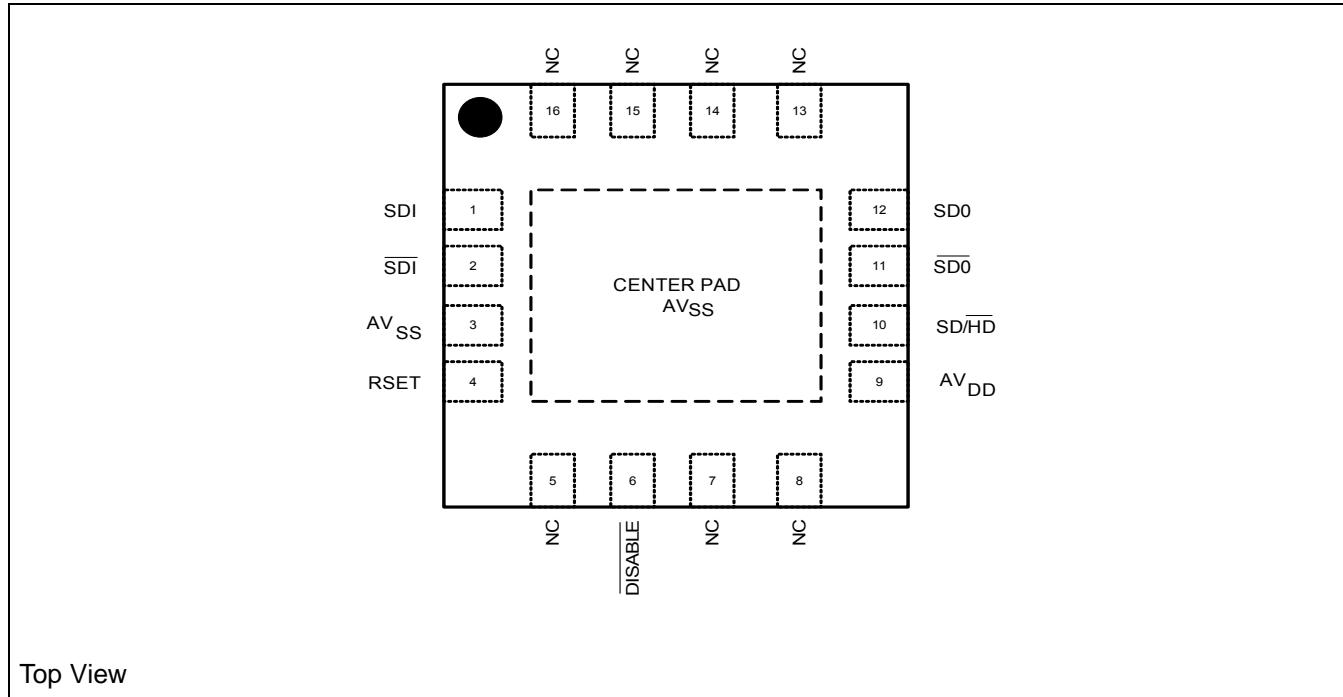

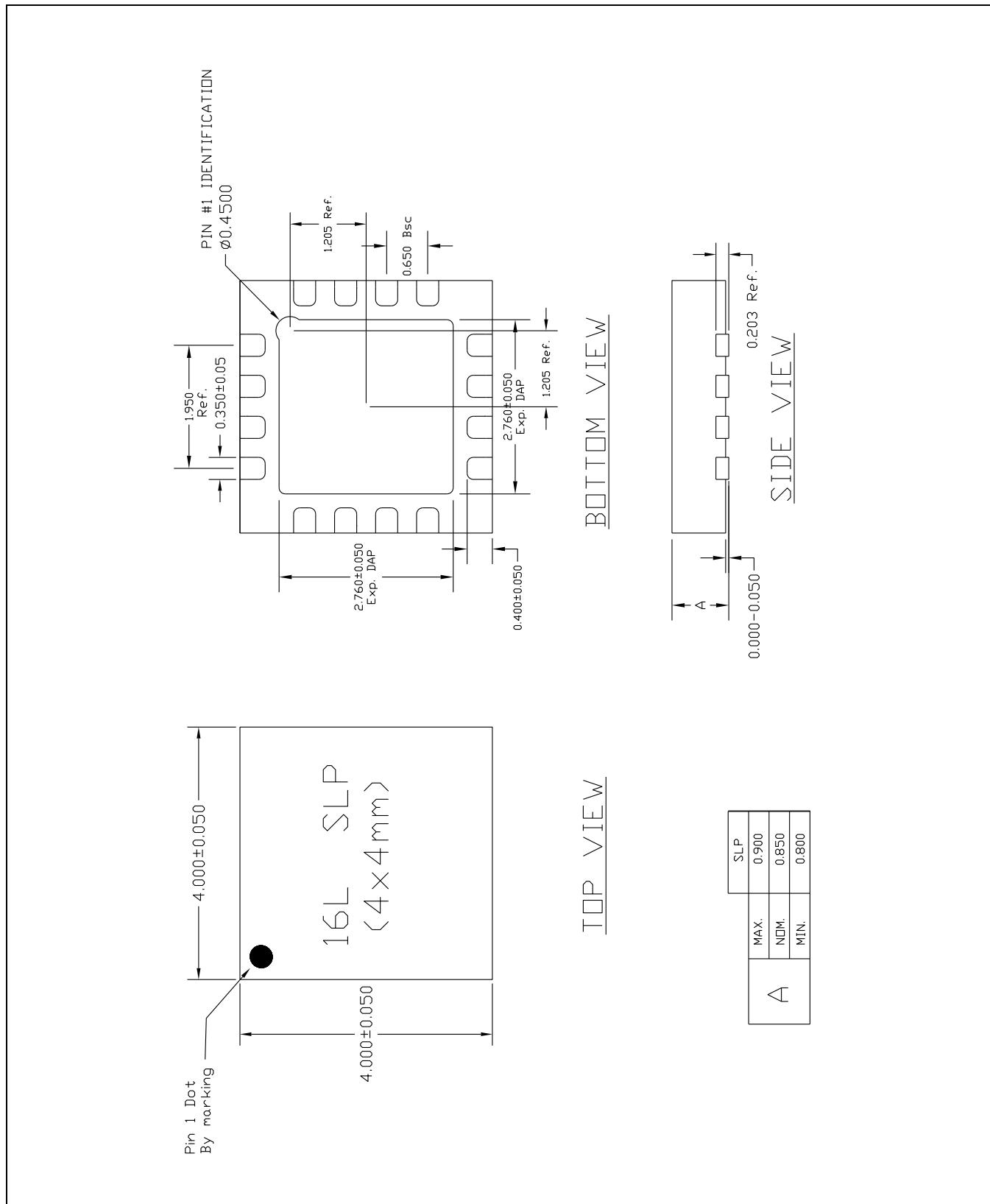

The M21328 is available in a 16 pin 4x4mm MLF IC package. The pin out is shown in [Figure 1-2](#) and the package drawing in [Figure 1-3](#).

**Figure 1-2. M21328 Pin Out**

**Figure 1-3. Package Drawing (4x4 mm MLF Package)**

## 1.6 Manufacturability

The values shown in this section may change; however, these are standard requirements.

### 1.6.1 Electrostatic Discharge

Tested per JESD22-A114. This device passes 2000V of ESD Human Body Model (HBM) testing.

Tested per JESD22-C101. This device passes 500V of ESD Charged Device Model (CDM) testing.

Tested per EIA/JESD78. This device passes 150mA of trigger current at 85°C during Latchup testing.

### 1.6.2 Peak Reflow Temperature

M21328G (RoHS compliant package): Peak reflow temperature is 260°C per JEDEC standards.

## 1.7 Design Considerations

See Digital Video Interfacing Application Note (212xx-APP-001-A) for guidance on the following:

- Component Placement and Layout

- Routing Considerations and Thermal Considerations

The M21328 consumes less power than legacy devices, therefore the M21328 will contribute less thermal energy resulting in a lower operating temperature.

## 2.0 Functional Description

---

### 2.1 Features

#### 2.1.1 HD-SDI and SD-SDI Slew-rate Selection

The output slew rate of the M21328 is selectable to conform with the different SD-SDI, HD-SDI, and 2xHD specifications. With **SD/HD** = Low, rise/fall time is typically 100 ps. The slew rate will vary depending on the output matching network and connector used.

With **SD/HD** = High, for standard definition (143 to 540 Mbps) applications, the rise/fall time is typically 600 ps, which is compliant with SMPTE 259M and SMPTE 344M.

#### 2.1.2 Output Amplitude Adjustment

A resistor connected to **RSET** pin is used to set the single ended output amplitude swing.

For SMPTE compliance, an external  $750\Omega \pm 1\%$  resistor at **RSET** to  $A_{VDD}$  is recommended for a swing level of 800mV within a tolerance that is less than  $\pm 10\%$  which meets SMPTE requirements. The output amplitude can also be adjusted to range from 500 to 1600 mVpp single ended using the following formula:

$$\text{Output Swing} = (600/\text{RSET}) [\text{RSET in k}\Omega] (\text{in mVpp, Single Ended})$$

The actual swing is set as a function of the IC supply voltage, the external termination voltage and the limitations are shown in [Table 2-1](#). In applications where a lossy matching or splitting networks are used, the M21328 offers additional gain of up to 1600 mVpp swings, so the output after the lossy network can be SMPTE compliant.

**Table 2-1. Output Swing vs. Supply and Termination Voltage**

| $A_{VDD}$ (V) | $A_{VDDTERM}$ (V) | Maximum Swing<br>(Single-ended mVp-p) | Minimum Swing<br>(Single-ended mVp-p) |

|---------------|-------------------|---------------------------------------|---------------------------------------|

| 3.3V          | 3.3V              | 1200 mV                               | 500 mV                                |

| 3.3V          | 5.0V              | 1600 mV                               | 500 mV                                |

## 2.2 Pin Definitions

### 2.2.1 High-speed Inputs

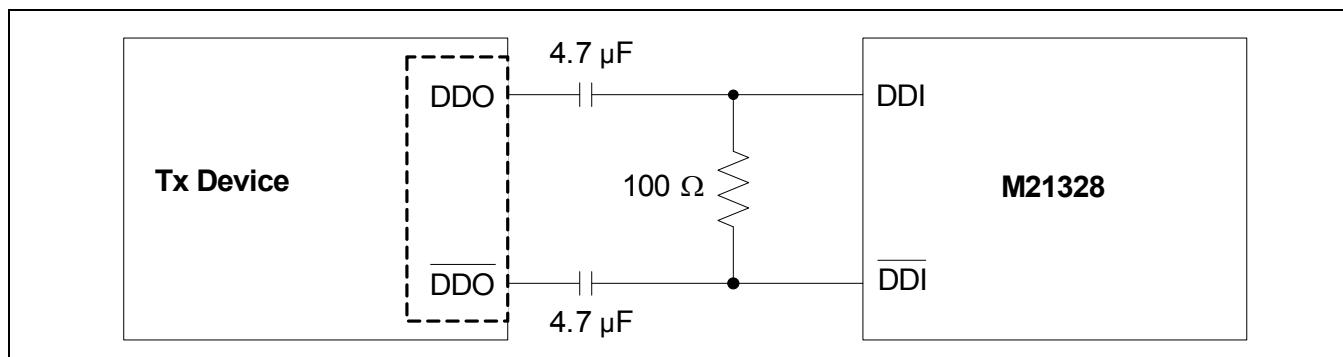

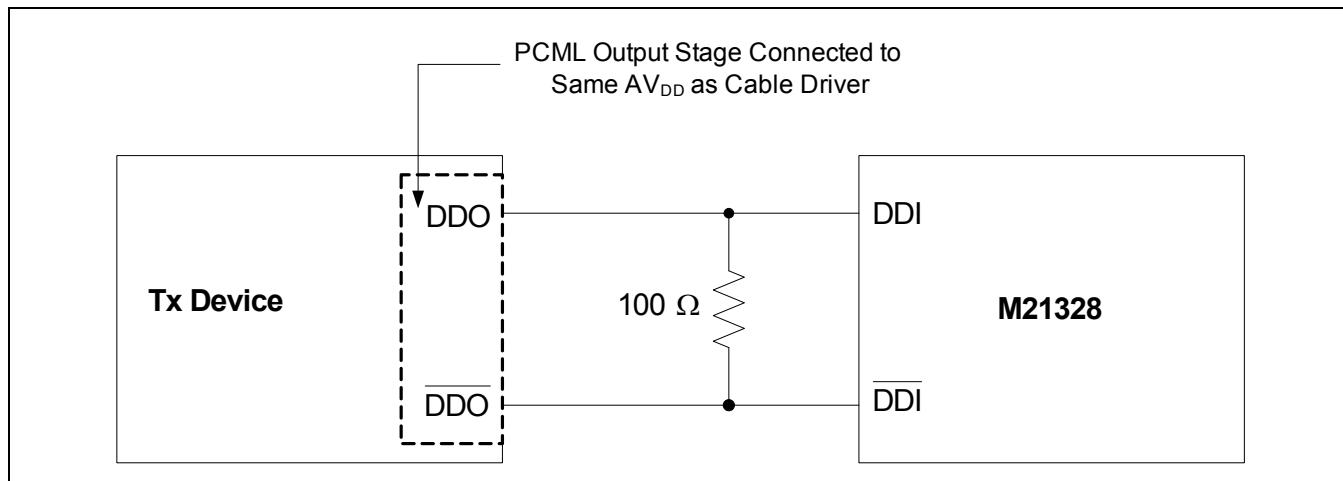

The M21328 is designed to be operated with input signals as low as 100 mV or up to 2000 mV differential peak to peak. The M21328 uses external  $50\Omega$  input termination resistors to match  $100\Omega$  differential impedance transmission lines for improved system level performance. The M21328 recommended input circuits are shown in [Figure 2-1](#) and [Figure 2-2](#).

Note that AC coupling is not required when the M21328 is driven by Mindspeed Broadcast video devices.

**Figure 2-1. Typical Input Circuit—AC Coupled**

**Figure 2-2. Typical Input Circuit—DC Coupled**

## 2.2.2 High-speed Outputs

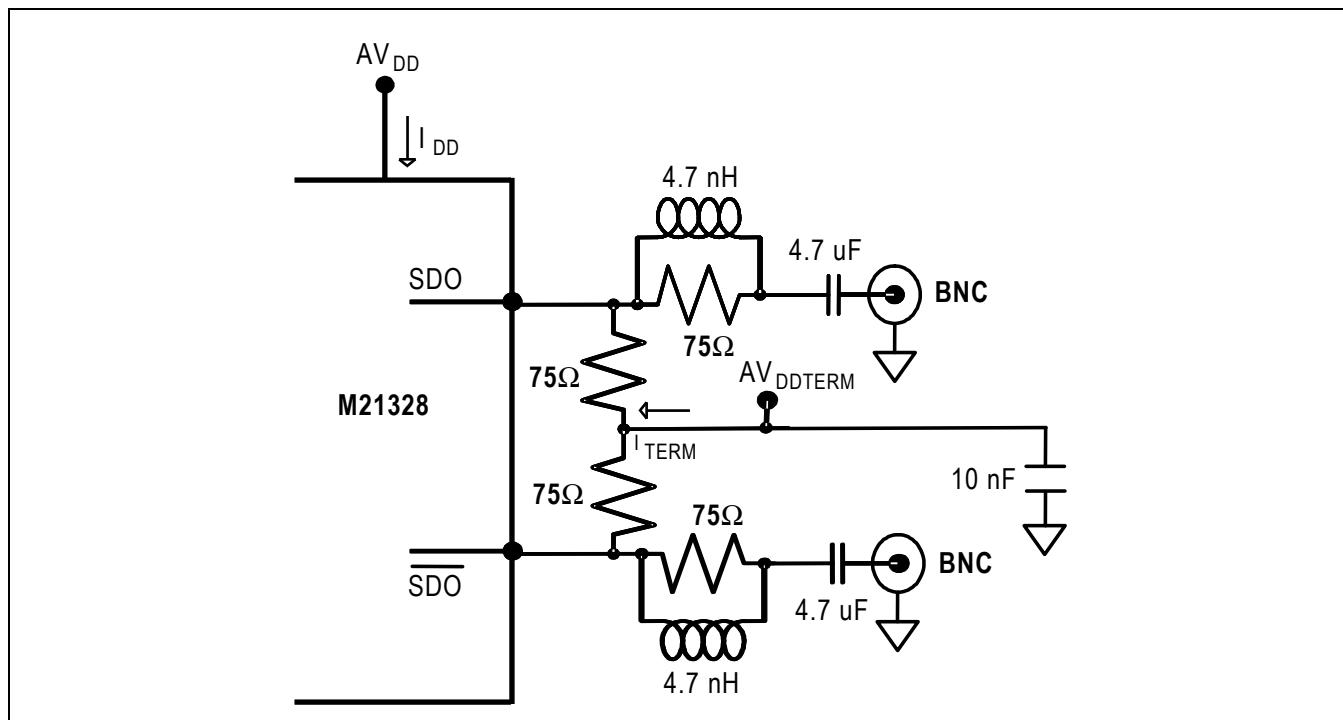

The M21328 output buffer is an open collector buffer that is designed for a return loss of 15 dB at SD and HD rates and 10 dB at 2xHD rates, using standard through-hole BNC connectors as typically employed in broadcast video equipment. A typical output matching circuit is shown in [Figure 2-3](#). The Output Return Loss (ORL) is dependent on many factors such as the value and type of components used, PCB layout, PCB trace lengths, and type of PCB di-electric, therefore, the recommendations in the figure below should be used as starting guidelines only. Different output matching network topologies and different component values will result in different ORL performance.

The M21328 has SD-SDI and HD-SDI rise/fall times that are typically faster than the legacy cable driver devices but within the relevant SMPTE specification for additional margin in most designs. The faster output slew rate results in a more open eye. The actual maximum output of the part depends on the applied IC voltage as well as the external termination voltage for the load termination. The limitations are discussed in [Section 2.1](#).

**Figure 2-3. Typical Output Matching/Back-termination Circuit**

## 2.2.3 M21328 Pin List

**Table 2-2. Interface Pins**

| Pin Name | Pin # | Function                                                                                                                                                                                                                                                              | Default | Type         |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|

| RSET     | 4     | Input control signal for setting the single-ended output swing amplitude.<br>Higher output swing levels or reduced variations with a $\pm 1\%$ tolerance external resistor.<br>For 800mVp-p single-ended, a $750\Omega \pm 1\%$ resistor to $AV_{DD}$ is recommended. | —       | Analog Input |

**Table 2-3. Power Pins**

| Pin Name   | Pin #                   | Function                                                                                       | Type  |

|------------|-------------------------|------------------------------------------------------------------------------------------------|-------|

| $AV_{SS}$  | 3                       | Chip Ground                                                                                    | Power |

| $AV_{DD}$  | 9                       | Positive Supply                                                                                | Power |

| NC         | 5, 7, 8, 13, 14, 15, 16 | Not Connected. Leave these pins floating. Do not connect to any supply, ground or logic level. | NC    |

| Center Pad | —                       | Chip Ground                                                                                    | Power |

**Table 2-4. High-speed Signal Pins**

| Pin Name             | Pin #  | Function                                                                       | Default | Type         |

|----------------------|--------|--------------------------------------------------------------------------------|---------|--------------|

| $SDI/\overline{SDI}$ | 1, 2   | Non-inverting and Inverting serial externally terminated inputs.               | —       | I—High-speed |

| $SDO/\overline{SDO}$ | 12, 11 | Non-inverting and inverting serial unterminated data outputs to coaxial cable. | —       | 0—High-speed |

**Table 2-5. Control Pins**

| Pin Name                                          | Pin # | Function                                                                                                                                                                                                              | Default | Type   |

|---------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|

| $SD/\overline{HD}$                                | 10    | Input control signal to change the output slew rate.<br>$SD/\overline{HD}$ = High: Slow output slew rate for SD-SDI rate (143–540 Mbps).<br>$SD/\overline{HD}$ = Low: Fast output slew rate for HD and 2xHD-SDI rate. | Pull-up | I—CMOS |

| $DISABLE$                                         | 6     | A low disables the $SDO/\overline{SDO}$ outputs.<br>A high enables the $SDO/\overline{SDO}$ outputs.                                                                                                                  | Pull-up | I—CMOS |

| <b>NOTES:</b>                                     |       |                                                                                                                                                                                                                       |         |        |

| Internal pull-ups/pull-downs are 100 k $\Omega$ . |       |                                                                                                                                                                                                                       |         |        |

## Appendix

---

### A.1 Glossary of Terms/Acronyms

|       |                                                    |

|-------|----------------------------------------------------|

| BER   | Bit Error Rate                                     |

| CD    | Cable Driver                                       |

| CDA   | Cable Distribution Amplifier                       |

| CML   | Current Mode Logic                                 |

| CMOS  | Complementary Metal Oxide Semiconductor            |

| DPLL  | Digital Phase Locked Loop                          |

| DTV   | Digital Television                                 |

| DVB   | Digital Video Broadcast                            |

| EMI   | Electro Magnetic Interference                      |

| EQ    | Equalizer or Equalization                          |

| GREEN | Environmentally friendly                           |

| HD    | High Definition                                    |

| HW    | Hardware                                           |

| IC    | Integrated Circuit                                 |

| ID    | Identifier                                         |

| I/O   | Input/Output                                       |

| MLF   | Micro Lead Frame package (also called QFN)         |

| PCB   | Printed Circuit Board                              |

| ORL   | Output Return Loss                                 |

| RoHS  | Restriction of Hazardous Substances                |

| SD    | Standard Definition                                |

| SDI   | Serial Digital Input                               |

| SDO   | Serial Digital Output                              |

| SE    | Single Ended                                       |

| SMPTE | Society of Motion Picture and Television Engineers |

## A.2 Reference Documents

### A.2.1 External

The following external documents were referenced in this data sheet.

- Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages

- Amkor Technology Thermal Test Report TT-00-06 (See <http://www.amkor.com> for detailed information)

- SMPTE 292M, SMPTE 259M, SMPTE 344M

- ESI TR101 891 DVB Asynchronous Serial Interface (ASI)

[www.mindspeed.com](http://www.mindspeed.com)

General Information:

Telephone: (949) 579-3000

Headquarters - Newport Beach

4000 MacArthur Blvd., East Tower

Newport Beach, CA 92660

© 2007-2009 Mindspeed Technologies®, Inc. All rights reserved.

Information in this document is provided in connection with Mindspeed Technologies® ("Mindspeed®") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Except as provided in Mindspeed's Terms and Conditions of Sale for such products or in any separate agreement related to this document, Mindspeed assumes no liability whatsoever. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.